相位噪声和抖动对系统性能的影响

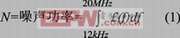

计算得到的是相位调制噪声在该频段内的功率,而相位调制正是造成抖动的原因。由此,我们还能用如下的定积分推出RMS抖动的值。

下式可求得该噪声功率造成的RMS抖动:

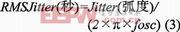

抖动值还可以用其他单位表示,例如单位时间(UI)或时间。将上式除以以弧度为单位的中心频率就可以将抖动单位转换为时间,见下式:

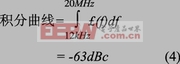

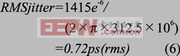

利用图4所绘的噪声功率值,我们可以计算一个312.5MHz振荡器的RMS抖动。将相位噪声曲线在12 kHz到20 MHz范围内积分,得到-63 dBc:

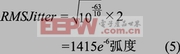

因此可以得到如下式所示的RMS相位抖动值,单位为弧度:

还可以将该抖动值单位转换为皮秒:

而同样的312.5 MHz振荡器的典性总抖动值在5ps RMS左右。

最终,我们计算得到的0.72 ps RMS的抖动值只在最大抖动中占很小的比例。

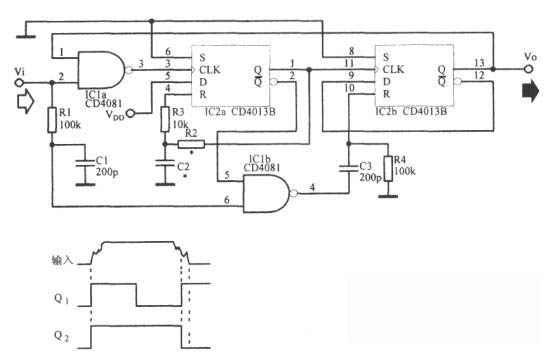

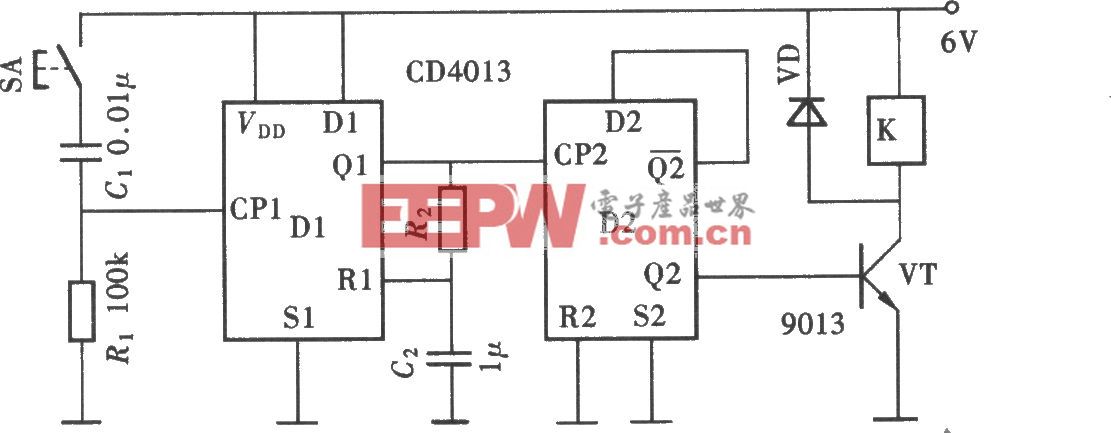

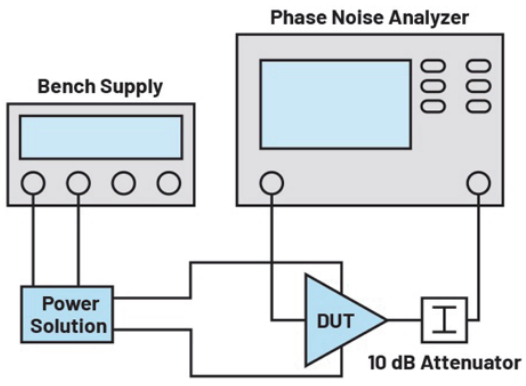

怎样将电路板上的相位噪声和抖动降至最低

电路板设计师可以通过两种关键技术降低板上的确定性信号抖动:

1.完全以差分形式收发信号:诸如LVDS或PECL等一些以差分方式收发信号的惯例,都能极大降低确定性抖动的影响,而且这种差分通路还能消减信号通路上的所有干扰和串扰。由于这种信号收发系统对共模噪声本来就有高度抑制能力,因此差分形式本来就有消除抖动的趋向。

评论