利用FFT IP Core实现FFT算法

3.3 求模运算器

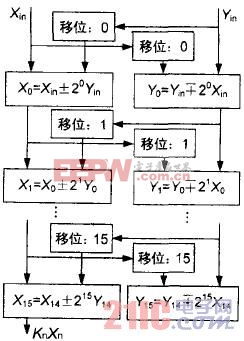

由于工程只要求求平方根,不涉及角度的计算,因此,CORDIC的角度计算部分没有给出,但这并不会影响到幅度的计算。整个CORDIC采用全流水线结构,设计总共有16级流水线单元,各流水线单元结构相似。CORDIC流水线结构如图3所示。

图3 CORDIC流水线原理图

该结果并不是最终结果,还要加一级幅度校正,以去除畸变因子的影响。

4 结束语

设计的输入和输出工作频率相对较低,因而很容易满足,关键是FFT Core的性能指标。根据工程需要,输入数据速率采用5MHz,FFT Core工作在40MHz,输出转换结果采用20MHz时钟,在此条件下对设计进行硬件测试,结果证明设计功能正确、工作稳定、性能优越。另外,经软件时序仿真可知,FFT Core最高工作频率可达到117.52MHz,通过提高运算时钟,还可获得更快的运算能力。

设计选用Altera公司的FFT Core,成功地在FPGA中实现了两路连续256点实数序列FFT的算法,其设计成本低、性能好,已经成功地应用到

雷达产品中。由于FFT Core的可塑性很强,通过改动参数设置,就可轻易地使设计适应于不同的产品。

评论