利用FFT IP Core实现FFT算法

Stratix II、Stratix GX、Stratix系列FPGA器件。该FFT Core功能是执行高性能的正向复数FFT或反向的FFT(IFFT),采用基2/4频域抽取(DIF)的FFT算法,其转换长度为2m,这里6≤m≤14。在其内部,FFT采用块浮点结构,以在最大信噪比(SNR)和最小资源需求之间获得最大的收益。FFT Core接收一个长度为N的、二进制补码格式、顺序输入的复数序列作为输入,输出转换域的、顺序的复数数据序列。同时,一个累加块指数被输出,表示块浮点的量化因子。FFT Core的转换方向事先由一个输入端口为每个数据转换块指定。

FFT Core可以设置两种不同的引擎结构:四输出(Quad-output FFT engine)和单输出(Single-output FFT engine)。对于要求转换时间尽量小的应用,四输出引擎结构是最佳的选择;对于要求资源尽量少的应用,单输出引擎结构比较合适。为了增加整个FFT Core的吞吐量,可以采用多并行引擎结构。

FFT Core支持3种I/O数据流结构:连续(streaming)、缓冲突发(Buffered Burst)、突发(Burst)。连续I/O数据流结构允许处理连续输入数据,输出连续复数数据流,而不中断输入和输出数据;缓冲突发I/O数据流结构与连续结构相比,需要更少的存储资源,但是,这是以减少平均吞吐量为代价的;突发数据流结构的操作与缓冲突发方式基本上一致,但突发方式则需要更少的存储资源,这也是以降低吞吐量为代价的。

3 硬件设计

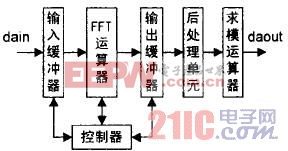

图1整体原理图

设计的整体原理图如图1所示。输入和输出缓冲器分别存储预处理数据和FFT转换结果;FFT运算器负责FFT运算;控制器为输入和输出缓冲器提供读写地址,并控制FFT运算的时序和缓冲器的读写操作;后处理单元从单路复数输入频谱数据中分离出两路实数输入频谱数据;求模运算器实现CORDIC算法,求取转换结果的平方根。设计的输入为两路实数序列,一路作为实部,另一路作为虚部,由连续的256点的数据段组成;输出是间断的256点数据段,各数据段的前128点为第一路的频谱数据,后128点是第二路的频谱数据。根据FFT频谱关于中心点对称的结果,只截取前半段频谱数据并不会丢失任何信息。

整个系统的工作时序为:

①数据以5MHz的速率输入到输入缓冲器;

②FFT运算器以40MHz的速率从输入缓冲器中取数进行运算;

③FFT运算结束时,将转换结果存入到输出缓冲器中;

④输出缓冲器数据以20MHz的速率被送到后处理单元进行转变;

⑤数据被送到求模运算器,进行CORDIC运算,输出;

⑥当③结束时,FFT运算器又回到起始状态,等待处理下一组数据,从而使运算周而复始地进行。整个设计由控制器严格控制。

输入和输出缓冲器由FPGA内部的RAM实现,这些都相对简单。下面重点介绍。FFT运算器、控制器、后处理单元和求模运算器。

评论