基于FPGA的运动估计设计

2.1 地址计数器模块

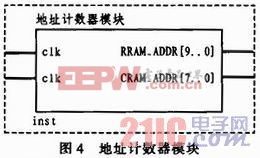

地址计数器主要是产生出可以在RRAM(参考块存储器)和CRAM(当前块存储器)中有目的地进行寻址的地址信号。如图4所示。本文引用地址://www.cghlg.com/article/190177.htm

地址计数器模块的设计与当前块和参考块的存储有很大的关系。将数据存入当前块存储器和参考块存储器时的顺序是由左到右,由下到上,即当前块存储器是(-7,-7),(-6,-7),(-5,-7)……(8,-7),(-7,-6),(-6,-6)……(8,7),(8,8)。而参考块存储器是(-15,-15),(-15,-14),(-15,-13)……(-15,16),(-14,-15),(-14,-14)……(16,15),(16,16)。则可知在寻址当前块存储器时可以直接按照地址的由左到右,由下到上累加。其计算公式如式(2)所示:

C_addr=(j+7)×16+(i+8) (2)

对于参考块存储器,它是一个32x32的数据块,设计的目的是从其中取出符合三步搜索法的9个数据块,当然这九个数据块都是16x16的,而且是以原点为中心组成的搜索点群。其计算公式如式(3)所示:

R_addr=(j+15)x32+(i+16) (3)

Clk是时钟频率信号,当它发生上升沿跳变时会使得产生的地址跳变到下一个新值。

Clr是清零信号,当它是低电平时,地址计数器可以产生从零开始的连续地址。

由于,当前块存储器只是一个16x16的RAM,其总的存储空间是256,则可知使用八位地址就可以进行寻址整个空间,即CRAM_ADDR是八位输出信号。而参考块存储器是一个32x32的的RAM,其总的存储空间是1 024,则可知使用十位地址就可以进行寻址整个空间,即RRAM_ADDR是十位输出信号。

2.2 参考块分频器模块

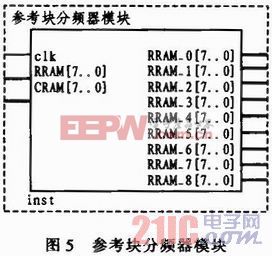

参考块分频器模块主要是将从参考块存储器中输出的信号经过分频处理后,存储在9个独立的单元,以便后续的处理,如图5所示。

由参考块输出的信号是256x9个连续的像素值,而当前块输出的信号只是256个连续信号在连续时钟驱动下的九次重复,这样就很难在256x9个时钟周期内完成对9个匹配块的处理,更难在256个时钟周期内完成。因此要通过参考块分频器将参考块存储器连续输出的256x9个像素点值进行九次分频,存储在9个RAM单元之中。这样当下一个时钟周期的上升沿到来时,这9个RAM可以同时输出信号,并在接下来的255个时钟周期之后将里面存储的所有信号输出,而且输出的这些信号相互之间是完全独立的。同时,为了使后面的各模块能够很好的进行,参考块分频器模块还引入了当前块的像素值信号,使得存入9个RAM单元的信号不仅仅是参考块的像素点值,还有当前块的像素点值以便保证后面的减法器可以正常工作。

评论