1553B总线中曼彻斯特编解码器的设计

2.1 编码过程

编码过程如下:

(1)检测编码周期是否开始,编码周期开始后将同步头类型、16位并行数据存储到内部寄存器中,与此同时计数器cnt开始计数。

(2)在计数器cnt的控制下通过码型生成器发出同步头、数据位、奇偶校验位。

(3)在当前字的曼彻斯特码发送完成后回到过程(1)等待发送下一个字

2.2 端口说明

rst_n为异步复位信号;clk为系统时钟,频率为信息传输速率的12倍;enc_trigger(输入,高有效)的编码开始的触发信号;enc_csw(输

入,高有效)表示要发送的字为命令字或状态字;enc_dw(输入,高有效)表示要发送的字为数据字;enc_data(输入)表示16位要发送的并行数据;tx_data_p(输出)表示发出的曼彻斯特原码;tx_data_n(输出)表示发出的曼彻斯特反码。

2.3 子模块说明

(1)6分频电路

将系统时钟6分频输出占空比为1/6的编码时钟使能信号enc_clk_en,该信号的频率为信息传输速率的2倍,其他3个模块只有在采样到该信号高电平后才会触发。在复杂时序电路设计中通过引入时钟使能信号可减少设计中的时钟信号,提高电路的可靠性。

(2)保持寄存器

在enc_clk_en有效且采样到enc_trigger为1时,将enc_csw,enc_dw,enc_data存入内部寄存器csw_reg,dw_reg,data_reg中。

(3)计数器

在enc_clk_en有效时采样到enc_trigger为1时,将计数使能信号置为1,并在其控制下开始计数,计数范围为0~39。

(4)码型生成器

码型生成器通过对16位并行数据data_reg做同或运算产生奇偶校验结果。在计数器cnt的控制下发送出曼彻斯特码。发送过程如下(以tx_data_p说明):

cnt(0~5):根据同步头类型,依次发送111000(csw_reg有效)或000111(dw_reg有效)。

cnt(6~37):发送数据位,在码元前半个周期发送原码,后半个周期发出反码。

cnt(38~39):发送奇偶校验位,计数到38时,发送奇偶校验位原码,39时发送其反码。

3 曼彻斯特解码器的设计

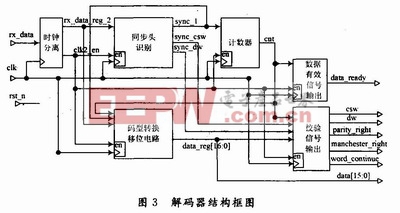

解码器需要将收到的曼彻斯特码解码,得出16位并行数据,并给出各种校验结果。本文设计的解码器逻辑结构如图3所示。本文引用地址://www.cghlg.com/article/187559.htm

评论