2.4GHz 0.35-μm CMOS全集成线性功率放大器设计

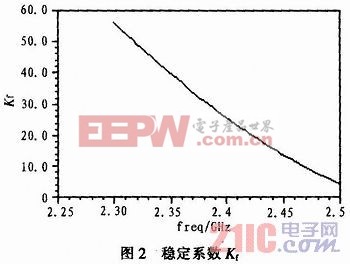

1.4 稳定性设计

由于集成电容和集成电感以及寄生电容的影响,集成电路在某些条件下形成自激,通过仿真为电路绘制稳定性圆,以此为依据修改电路图。修改后仿真稳定性参数,Kf>1。仿真参数如图2所示。进行稳定设计后,输入0 dBm功率信号时,输出功率为25.22dBm。本文引用地址://www.cghlg.com/article/187415.htm

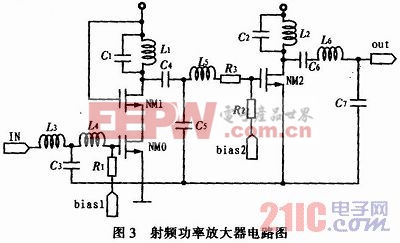

2 射频放大器电路结构设计

本射频功率放大器采用两级设计,电路如图3所示。第一级的共源共栅结构是模拟电路中常采用的一种电路设计技术,它能大幅提高输出阻抗,很大程度上提高电压增益,降低输入级的Miller效应,提高输入和输出的隔离度,降低晶体管击穿电压的压力,但此结构在一定的击穿电压和供电电压的情况下,降低了输出电压摆幅。第二级采用共源结构实现功率放大,这种结构可以充分利用大电压摆幅,降低对输出电流的要求,一定程度上减少晶体管的直流损耗。

在放大电路中NM1、NM2、L1、C1构成第一级放大,M1、M2组成共源共栅结构,L1在低频时提供直流偏置,在高频时与C1谐振,形成高阻抗。如果要L1与M2漏极寄生电容和后级输入电容谐振,L1无法片上集成,再者电路整体性能变差。L3、L4、C3构成T形匹配网络,提供合理的S11参量,C4起到两级电路间交流耦合的作用,L5、C5是级间匹配网络,提供级间最佳功率传输。NM3、L2、C2构成输出级,提供大功率输出,L2、C2在高频时谐振,提供高输出阻抗。由于L2只与M3漏极寄生电容谐振,L2很大,占用芯片面积较大,所以另加电容C2,以减少L2的量值。C6是隔直电容,L6、C7是输出匹配网络,提供最优输出功。

评论