LVDS技术在数字视频传输系统中的应用

ROUT[O:17]:解码器输出的18位并行LVTTL信号;

RCLK:解码器输出时钟,当解码器正常工作时,该时钟与输入的解码时钟REFCLK同频率;

LOCK:解码器工作状态指示信号,当解码器工作不正常时,该信号为高电平,通过检测该信号可以测出系统传输的误码率;

LINE_LE、LOCAL_LE:回馈信号,可以用于器件工作状态检测,实际应用中置低电平;

AVDD:模拟供电电源,3.3V供电;AGND:模拟地;

DVDD:数字供电电源,3.3V供电;DGND:数字地;PVDD:锁相环供电电源,3.3V供电;PGND:锁相环地。

1.2.2 缓冲器和均衡器

虽然LVDS串行/解串器可以驱动连接电缆,但电缆的长度受到一定的限制,一般不超过几米。由于本系统需要长距离传送数据,因此为了解决长距离传送的设计问题,考虑在发送单元和接收单元的高速串行数字信号进行预加重和均衡。预加重功能不但可为高频电缆的损耗提供补偿,而且也可加强电缆及背板的数据传送能力,使系统可以支持更长距离的传送。均衡器的功能是对信道损失进行补偿并滤除噪声,使电缆传来的串行数字信号可以重新恢复其原有强度。本文引用地址://www.cghlg.com/article/166594.htm

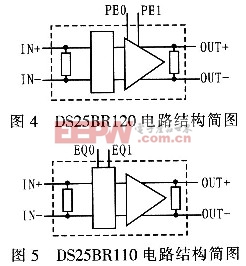

采用单通道LVDS缓冲器DS25BRl20和DS25BRll0,即使传输速度高达3.125Gb/s,仍可确保信号完整无缺。DS25BRl20和DS25BRllO的结构简图如图4和图5所示,其中DS25BRl20具有四级传输预加重功能,可通过设置PE0、PEl选择不同的预加重等级;DS25BRll0具有四级接收均衡功能,可通过设置EQ0、EQl选择不同的均衡等级。这两款器件均内置有100Ω的输入输出终端匹配电阻,因此可直接与串行/解串器DS92LVl8输出和输入端相连,不必考虑外接匹配电阻的问题,减少了外围器件的数量,简化了PCB布线。

2 数字视频传输系统的实现

在本系统中,传输的数字图像分辨率为512x256x10 bit,编码时钟和解码时钟均选用40 MHz。在设计过程中,发送单元和接收单元均为4层板,从顶层到底层分为LVDS信号层、地层、电源层、TTL信号层,采用屏蔽双绞线电缆相连。LVDS信号不仅是差分信号,也是高速数字信号,因此在进行含有LVDS信号的PCB设计时,如何实现阻抗匹配,以防止信号在传输线终端产生反射是非常重要的。否则,由差分阻抗的不匹配产生的反射不仅会减弱信号,还会增加共模噪声,从而产生电磁辐射。因此布线时应注意:1)LVDS缓冲器DS25BRl20和均衡器DS25BRllO应尽可能地靠近DS92LV18输出和输入端;2)差分线对的长度相互匹配,差分线对内两条线之间的距离应尽可能短且两条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性:3)LVDS信号走线应尽量短而直,需拐弯时应走圆弧或45°折线,并尽量减少过孔。4)使用分布式的多个电容来旁路LVDS设备,表贴电容尽可能靠近电源/地层引脚放置。对于DS92LVl8,若PVDD(锁相环供电电源)与AVDD、DVDD没有隔离使用同一个电源时,则应贴近每一个PVDD引脚旁放一π型(CRC或CLC)滤波器进行滤波。

经过实验,该数字视频传输系统在数据传输时解串出的数据无误码,解串出的时钟和行场等同步信号与原信号相比有极小的相位延迟,恢复的图像清晰无干扰,实现了视频图像的实时传输,满足工程应用要求。如果接收板解串的图像需要进行后续的图像处理,则建议在接收板的解串器后增加一片FPGA,将解串的并行信号接入FPGA在时序上进行处理如进行相位对齐等,则效果会更好。

3 结论

随着高分辨率、远距离数字视频传输的需求急剧增加,LVDS技术以其高速传输能力、低噪声干扰、集成能力强、低成本、低功耗等特点,必将具有广阔的应用前景。文中设计的基于LVDS技术的视频传输系统,实现了数字视频的实时远距离传输,方案通用性和可扩展性强,可应用到更高帧频和分辨率的视频传输系统,也可应用到多路视频传输系统,满足数字视频传输的工程应用要求。

评论