LVDS技术在数字视频传输系统中的应用

1.2.1 串行/解串器

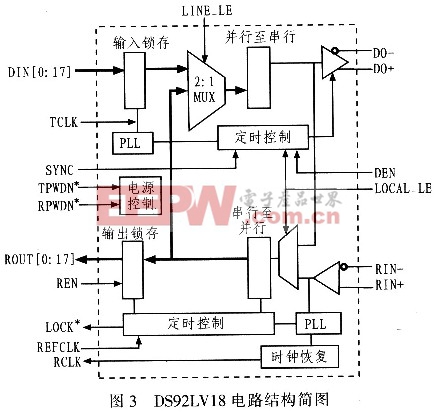

串行器和解串器采用18位高性能串行/解串器DS92LV18,其主要性能特点:时钟频率15~66 MHz,可支持0.27~1.188 Gb/s的有效载荷;收发一体设计,内置发射/接收数字锁相环,提供帧同步、帧检测、时钟恢复功能;具有“即插即用”的同步操作能力,带电插接时无需系统干预。DS92LV18在系统的发送单元中主要是将数字图像数据、时钟和同步等信号由并行转为串行的LVDS信号,在接收单元中主要将串行的LVDS信号数据解串恢复成并行的图像数据、时钟和同步信号。图3为DS92LVl8的结构简图。

DS92LVl8的引脚配置如下:

DIN[0:17]:18位并行LVTTL/LVCOMS输入数据信号;

TCLK:编码时钟,当编码器工作时,该时钟信号经编码锁相环20倍频后将DIN[0:17]和TCLK编码成20位串行数据信号,以LVDS标准电平信号从D0+和DO-输出,应用中要求与解码时钟REFCLK同频率,2个时钟频率偏差不能超过5%;

SYNC:编码器工作控制信号,当编码器和解码器工作时,置低电平;

TPWDN、DEN:编码器工作控制信号,当编码器工作时,置高电平;当解码器工作时,置低电平;

RPWDN、REN:解码器工作控制信号,当解码器工作时,置高电平:当编码器工作时,置低电平;

RIN+、RIN-:解码器输入串行LVDS信号;

评论