基于 FPGA 的原型

基于 FPGA 的 ASIC 原型可快速、准确地实现 SoC 系统建模和验证并加速软件和固件的开发。Xilinx 以其 20nm 解决方案将原型设计提升到新的水平, Virtex UltraScale VU440 FPGA 及 28nm Virtex®-7 2000T FPGA现已投入批量生产。数百万逻辑单元解决方案:

● 避免了进行多芯片分区的困扰

● 减少了大型 ASIC 和 ASSP 设计的开发风险

● 减少了板级空间的要求和复杂性

● 实现灵活 I/O,创建邻接器件

● 降低了系统级功耗

Virtex UltraScale 440: 世界最大容量 FPGA

Virtex UltraScale 440 器件基于第二代 堆叠硅片互联 (SSI)技术 系统容量是同类产品的 4 倍:

● 4.4M 逻辑单元、 20B 晶体管

● 48 个 16.3Gb/s 串行收发器

● 89Mb BRAM

● 1,456 个 I/O

查看 设计范例。

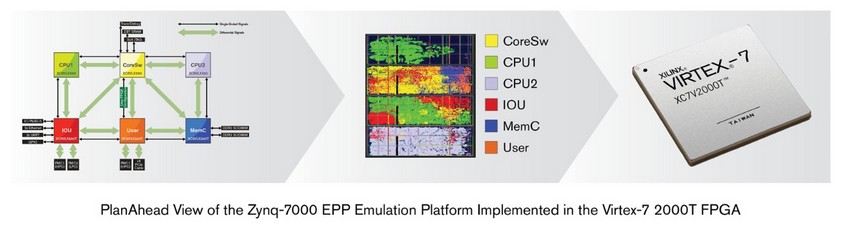

Virtex-7 2000T: 利用 ASIC 原型构建

Virtex-7 2000T FPGA 通过 堆叠硅片互联 (SSI)实现,适合 ASIC 原型设计及仿真:

● 2M 逻辑单元、 6.8B 晶体管

● 36 个 12.5Gb/s 串行收发器

● 46Mb BRAM

● 1,200 个 I/O

● 现已批量生产

ASIC 仿真实现

Xilinx 充分利用 ASIC 原型设计和仿真方法来创建 Zynq™-7000 SoC 仿真平台。 基于 Virtex-5 和 Virtex-6 的原仿真平台被移植到 Virtex-7 2000T FPGA,性能提升 5 倍,器件减少 6 倍。

观看视频。