- 台积电的 5nm 和 3nm

工艺是该公司在市场上"最热门"的产品之一,据报道,这家台湾巨头的利用率达到了

100%。众所周知,台积电是迄今为止半导体行业中最具主导地位的公司之一,原因很简单,因为英特尔代工厂和三星等竞争对手在产品供应方面有所懈怠,这就使得这家台湾巨头可以充分利用不断涌现的需求。根据Ctee的报道,台积电预计到明年5纳米生产线的利用率将达到100%,理由是人工智能行业的需求将大幅上升。 这一进展充分显示了台积电在现代市场中的主导地位,不给竞争对手任何空间。台积电

- 关键字:

台积电 5nm 3nm

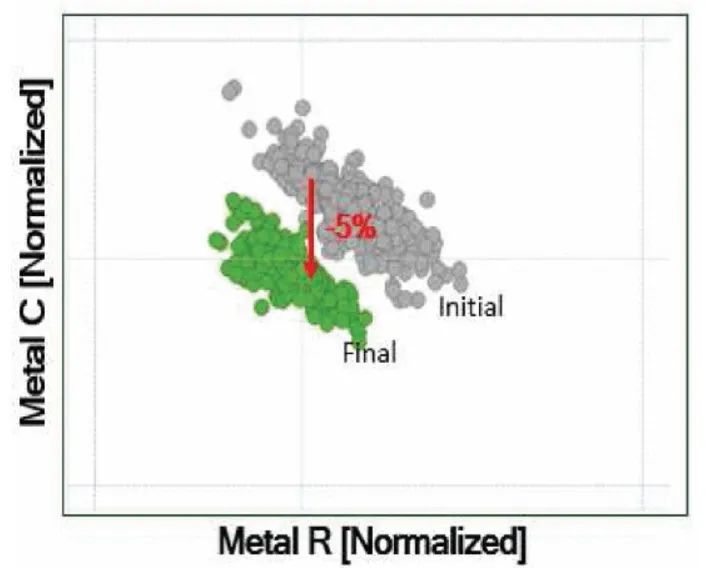

- 6月17日,据台媒《工商时报》报道,在产能供不应求的情况下,台积电将针对3nm/5nm先进制程和先进封装执行价格调涨。其中,3nm代工报价涨幅或在5%以上,而2025年度先进封装报价也将上涨10~20%。

- 关键字:

台积电 制程 封装 3nm 5nm 英伟达 CoWoS

- 在 HBM4 内存带来的几大变化中,最直接的变化之一就是内存接口的宽度。随着第四代内存标准从已经很宽的 1024 位接口升级到超宽的 2048 位接口,HBM4 内存堆栈将不会像以前一样正常工作;芯片制造商需要采用比现在更先进的封装方法,以适应更宽的内存。作为

2024 年欧洲技术研讨会演讲的一部分,台积电提供了一些有关其将为 HBM4

制造的基础模具的新细节,这些模具将使用逻辑工艺制造。由于台积电计划采用其 N12 和 N5 工艺的变体来完成这项任务,该公司有望在 HBM4

制造工艺中占据有

- 关键字:

台积电 12nm 5nm 工艺 HBM4 基础芯片

- 4 月 11 日消息,Meta 公司于 2023 年 5 月推出定制芯片 MTIA v1 芯片之后,近日发布新闻稿,介绍了新款 MTIA 芯片的细节。MTIA v1 芯片采用 7nm 工艺,而新款 MTIA 芯片采用 5nm 工艺,采用更大的物理设计(拥有更多的处理核心),功耗也从 25W 提升到了 90W,时钟频率也从 800MHz 提高到了 1.35GHz。Meta 公司表示目前已经在 16 个数据中心使用新款 MTIA 芯片,与 MTIA v1 相比,整体性能提高了 3 倍。但 Meta 只主动表示

- 关键字:

Meta MTIA 芯片 5nm 工艺 90W 功耗 1.35GHz

- 关于英特尔Gaudi 3的“中国特供版” AI 芯片有了新进展。4月15日消息,芯片巨头英特尔(Intel)日前在官网发布一份24页的“Gaudi 3 AI加速器白皮书”中披露,英特尔将推出Gaudi 3在中国发售的两款“特供版”AI 芯片产品。英特尔Gaudi 3 AI芯片(图片来源:Intel官网)具体包括两种硬件形态加速卡:一款型号为HL-328的OAM兼容夹层卡(Mezzanine Card),预计将于今年6月24日推出;另一款是型号为HL-388的PCle加速卡,预计将于今年9月24日推出。而基

- 关键字:

英特尔 5nm AI

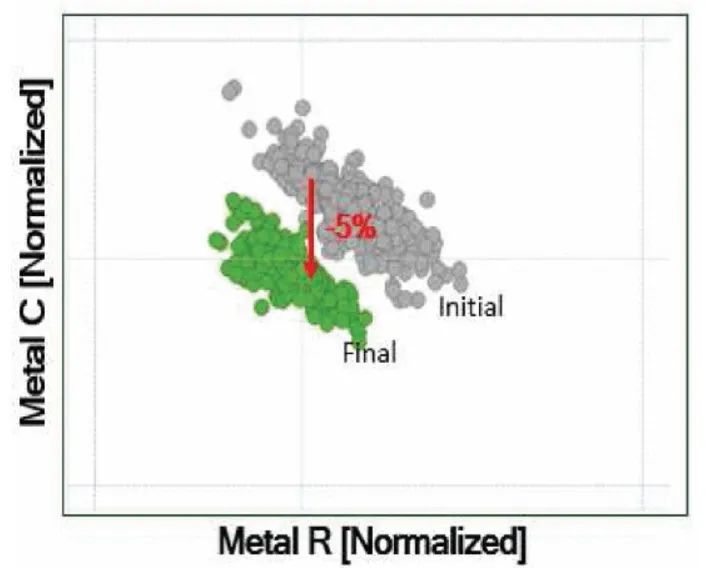

- ● 介绍随着技术推进到1.5nm及更先进节点,后段器件集成将会遇到新的难题,比如需要降低金属间距和支持新的工艺流程。为了强化电阻电容性能、减小边缘定位误差,并实现具有挑战性的制造工艺,需要进行工艺调整。为应对这些挑战,我们尝试在1.5nm节点后段自对准图形化中使用半大马士革方法。我们在imec生产了一组新的后段器件集成掩膜版,以对单大马士革和双大马士革进行电性评估。新掩膜版的金属间距分别为14nm、16nm、18nm、20nm和22nm,前两类是1.5nm节点后段的最小目标金属间距

- 关键字:

半大马士革 后段器件集成 1.5nm SEMulator3D

- 5月22日消息,在半导体领域,印度也燃起了雄心,此前没啥基础的他们都要励志在5年内做全球第一的半导体大国,而且全产业链发展,印度高性能计算中心C-DAC本周就公布了自己研发的Aum HPC处理器,最多96核,而且是5nm工艺。在高性能计算市场,ARM处理器近年来确实取得了一些成绩,富士通研发的48核A64FX处理器之前还成为TOP500超算第一,NVIDIA也有72核到144核的Grace处理器,Ampere公司之前推出了80核的ARM处理器。这几天Ampere还推出了新一代的云数据中心处理器“Amper

- 关键字:

印度 96核 5nm

- 据《科创板日报》报道,针对“因4~5纳米先进制程良率逐渐稳定,客户订单正逐渐增加,稼动率也相应反弹,12英寸稼动率回升至九成。”这一市场消息,三星半导体对其进行了回应。报道指出,三星半导体相关负责人回应表示,“暂无法透露最新良率或者客户情况。正如我们在2022年4月的财务电话会议上所提及,5nm制程良率自去年年初以来已稳定下来,而4nm制程良率也已得到了提升,自2022年第一季度以来一直在预期的轨道上。自此4~5nm制程良率已经稳定了。”据韩国媒体BusinessKorea报道,三星4纳米制程良率相较之前

- 关键字:

5nm 良率 晶圆代工 三星

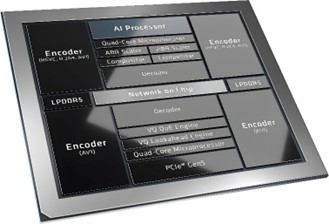

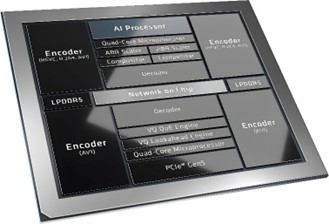

- 2023 年 4 月 6 日,加利福尼亚州圣克拉拉 — AMD (超威,纳斯达克股票代码:AMD)今日宣布推出 AMD Alveo™ MA35D 媒体加速器,该卡具备两个 5 纳米基于 ASIC 的、支持 AV1 压缩标准的视频处理单元( VPU ),专为推动大规模直播互动流媒体服务新时代而打造。随着全球视频市场超 70% 的份额由直播内容主导1,一类新型的低时延、大容量交互式流媒体应用正在涌现,例如连线观赏、直播购物、在线拍卖和社交流媒体。 AMD Alveo MA35D 媒体加速器Alveo

- 关键字:

AMD 5nm ASIC 媒体加速器卡 大规模交互式流媒体服务

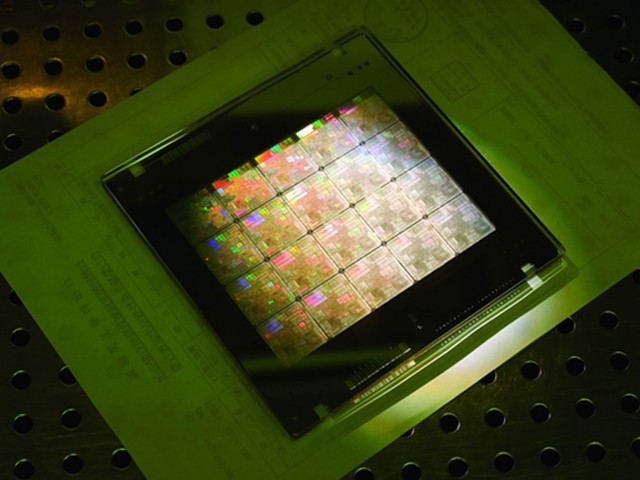

- 本文将解析使 3D NAND、高级 DRAM 和 5nm SoC 成为可能的架构、工具和材料。要提高高级 SoC 和封装(用于移动应用程序、数据中心和人工智能)的性能,就需要对架构、材料和核心制造流程进行复杂且代价高昂的更改。正在考虑的选项包括新的计算架构、不同的材料,包括更薄的势垒层和热预算更高的材料,以及更高纵横比的蚀刻和更快的外延层生长。挑战在于如何以不偏离功率、性能和面积/成本 (PPAC) 曲线太远的方式组合这些。当今的顶级智能手机使用集成多种低功耗、高性能功能的移动 SoC 平台,包括一个或多

- 关键字:

3D NAND DRAM 5nm SoC

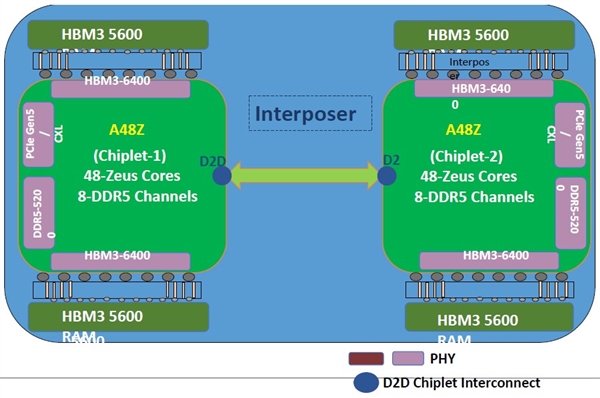

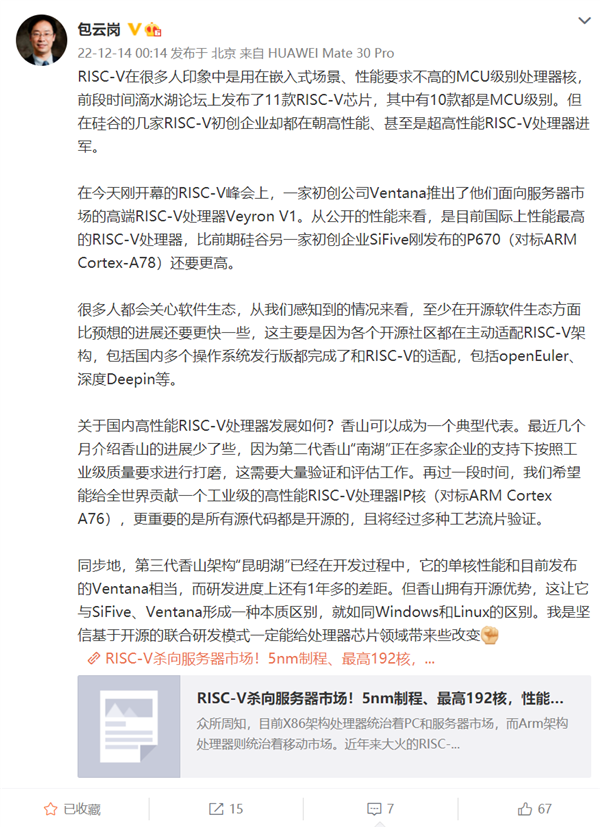

- 作为仅次于x86、ARM的第三大CPU架构,RISC-V凭借开源、免费的优势迅速发展,之前主要用于低功耗市场,但是现在也开始冲击高性能领域,Ventana公司日前已经做出了5nm 192核的芯片。Ventana公司日前发布了第一款产品Veyron V1,该公司研发了一种高性能RISC-V架构,每个CPU模块中有16个RISC-V内核,频率3.6GHz,整合48MB缓存,整个处理器可以集成12个CPU模块,做到192核,台积电5nm工艺生产制造,还有自己开发的高性能IO核心,延迟低至7ns,接近原生核心性能

- 关键字:

RISC-V 5nm 192核

- 概伦电子宣布其高性能并行SPICE仿真器NanoSpice™通过三星代工厂5nm工艺技术认证,满足双方共同客户对高精度、大容量和高性能的高端电路仿真需求。三星5nm工艺可以提高良率、降低功耗并改善性能,这就需要更高精度的电路仿真和验证工具来实现更优化的先进IC设计。NanoSpice™的认证属于三星代工厂的EDA认证项目,该仿真器可支持最新版的OMI接口(开放模型接口),在模拟IP的大规模后仿网表仿真中表现出良好的仿真收敛性和准确性,帮助双方共同客户充满信心地设计,缩短设计周期的同时确保更高精度。作为新一

- 关键字:

概伦电子 NanoSpice™ 5nm

- Credo Technology(纳斯达克股票代码:CRDO)近日正式宣布推出其基于台积电5nm及4nm制程工艺的112G PAM4 SerDes IP全系列产品,该系列能够全面覆盖客户在高性能计算、交换芯片、人工智能、机器学习、安全及光通信等领域的广泛需求,包括:超长距(LR+)、长距(LR)、中距(MR)、超极短距(XSR+)以及极短距(XSR)。 Credo IP产品业务开发助理副总裁Jim Bartenslager表示, “Credo先进的混合信号以及数字信号处理(DSP)1

- 关键字:

Credo 台积电 5nm 4nm SerDes IP

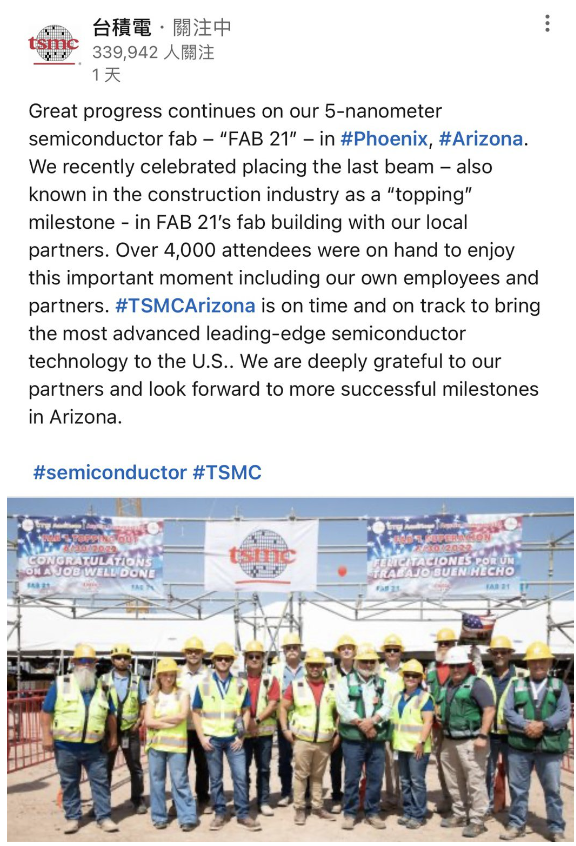

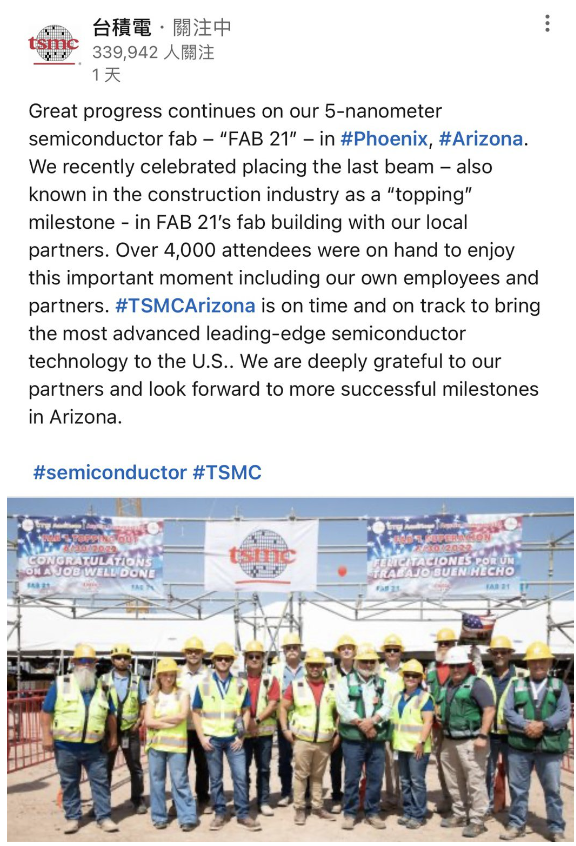

- IT之家7 月 28 日消息,两年前,台积电宣布将投资数十亿美元,在美国亚利桑那州厂建立 5nm 晶圆厂。该工厂于 2021 年 4 月动工兴建,预计 2024 年营运量产,月产能 2 万片。昨日,台积电为该工厂举行了上梁典礼。台积电的领英(linkedin)账号显示,本次上梁典礼有 4000 多名台积电员工及合作伙伴参加,他们一起庆祝了台积电 5nm 工厂的新里程碑。该典礼的举行意味着该工厂的基础设施全部完工,即将开始安装设备进行调试。该工厂未来产能以 5nm 工艺为主,这将是美国最先进的半导体工艺。此

- 关键字:

台积电 5nm 美国

- 芯研所7月15日消息,2020年台积电宣布将在美国建设晶圆厂,这是他们首次在海外建设先进工艺的5nm工厂,总投资计划高达240亿美元,目前还在建设中。在美国建设晶圆厂的成本是要高于亚洲地区的,在今天的Q2财报会议上,台积电也谈到了这个问题,表示仍处于工厂的建设阶段,美国工厂的成本比我们预期的要高。芯研所采编台积电表示,我们将这些信息提供给了当地政府,让他们全面了解成本差距,台积电仍在努力争取政府补贴,将继续努力降低成本。此前美国推出了高达520亿美元的半导体补贴法案,很多半导体公司都在争取这一补贴,不过这

- 关键字:

台积电 晶圆代工 5nm

5nm介绍

您好,目前还没有人创建词条5nm!

欢迎您创建该词条,阐述对5nm的理解,并与今后在此搜索5nm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

必威娱乐平台

杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473