RDMA IP开发的目的

本IP开发的目的是研究一款适合于FPGA端的通用性强,性能优越的RDMA IP

开发。它支持点对点,如两FPGA之间,FPGA与PC之间。与PC之间高速通信只需

一根光纤。当然,PC端需要转接卡,将光纤转入PC端,例如100G的CX455A-ECAT

100Gbe 网卡 就可以)。

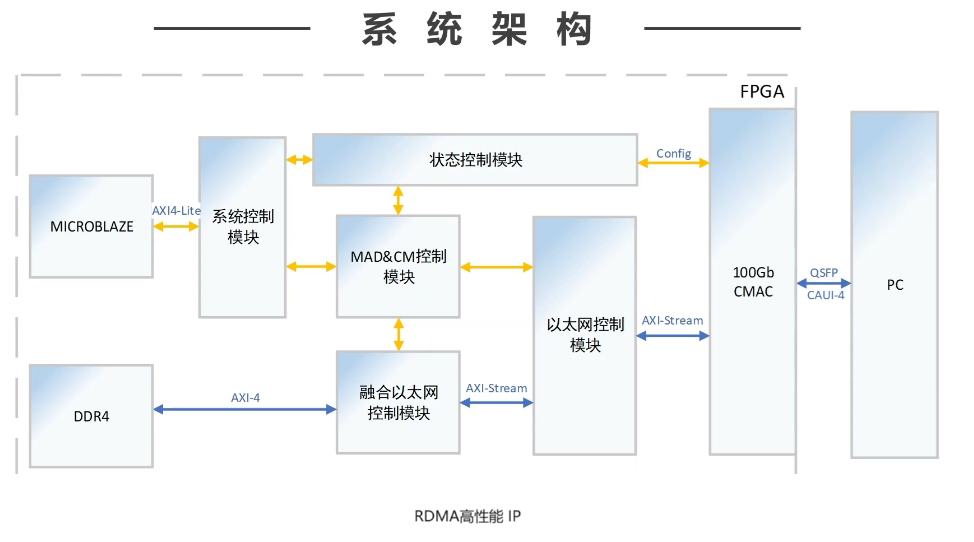

## RDMA架构

该架构如下:

本系统选用VCU118,虽然IP是纯逻辑设计,但还需要配合测试的简单控制。

故对IP的简单控制由Microblaze完成,如果是zynq系列,直接在arm核内完成,

DDR负责读写等数据缓存。该结构也是便于后续NVMe oF 开发。

## 性能测试

在xilinx开发平台测试,网卡支持100G,选用的是CX455A-ECAT 100Gbe。

支持RDMA RoCE v2协议。

实测数据:

SEND 71 Gbps

READ 91 Gbps (PC端给FPGA发包,受PC性能限制多一点)

WRITE 96 Gbps

R/W 延迟: 64B@95% 小于5 us

感兴趣的请看视频:

https://www.bilibili.com/video/BV1mPV5eCE8z/?spm_id_from=333.337.search-card.all.click

或者B站搜用户名:专注与守望 或内容 RDMA IP