基于CPLD的CCD驱动时序电路设计

电荷耦合器件(CCD),是一种以电荷为信号载体的光电传感器。他具有光电转换,电荷存储,转移和检测等功能。广泛应用于图像拍摄、传真通信系统,光学字符识别、广播TV、工业检测与自动控制、生物标本分析、天文观测等领域中[1]。CCD的外围电路比较复杂,往往给使用者带来不便,特别是驱动时序电路的实现,这是CCD应用的关键问题。早期的CCD驱动电路几乎全部是由普通数字电路芯片实现的,由于需要复杂的三相或四相交迭脉冲,一般整个驱动电路需要20个芯片左右,体积较大,设计也复杂,偏重于硬件的实现,调试困难,灵活性较差。除了数字电路芯片实现驱动方法外,还有单片机驱动方式,在这种设计方法中,硬件电路非常简单,但是存在资源浪费较多,频率较低的缺陷。采用复杂可编程逻辑器件CPLD技术,结合长安大学光电应用研究所的相关项目对CCD器件TCDl200D进行了驱动时序电路的设计与实现,该方法开发周期短,并且驱动信号稳定、可靠。系统功能模块完成后可以先通过计算机进行仿真,再实际投入使用,降低了使用风险性。

本文引用地址://www.cghlg.com/article/79038.htm可编程逻辑器件(PLD)是在20世纪80年代迅速发展起来的一种新型集成电路,随着大规模集成电路的进一步发展,出现了PAL和GAL逻辑器件,而复杂可编程逻辑器件CPLD是在此逻辑器件基础上发展起来的,跟分立元件相比,具有速度快、容量大、功耗小、集成度高、可靠性强等优点。故CPLD被广泛应用于各种电路的设计中。

l TCDl200D简介

1.1 TCDl200D的特点

TCDl200D是日本东芝公司生产的双沟道线阵CcD器件,具有灵敏度高(饱和曝光量为0.037 x·s)、暗电流低等特点。该器件具有2 160个像元,内部信号预处理电路包含采样保持和输出预放大电路,当温度为25℃时,该器件工作在5 V驱动脉冲,12 V电源条件下。

1.2 TCDl200D驱动时序要求

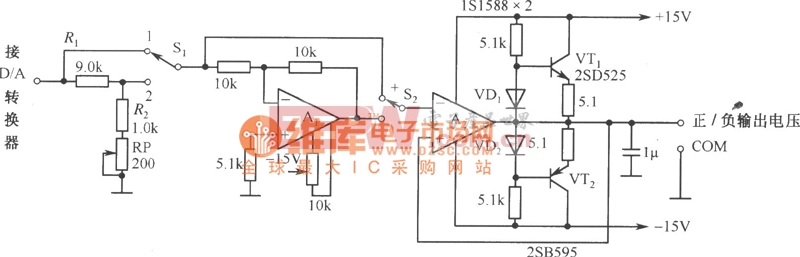

芯片正常工作需要4路驱动信号:时钟脉冲Fl,时钟脉冲F2,转移脉冲SH和复位脉冲RS。其中SH为光电荷转移脉冲,其下降沿是每行输出的起始点;F1,F2为两相交变驱动脉冲(相位差为90。),其作用为驱动信号电荷进行定向转移;RS为输出极复位脉冲,清除输出即输出一个单元电荷后所剩电荷,以保证下一个单元电荷电压的正确输出。在4路脉冲的正确驱动下,该图像传感器将产生有效光电信号OS和补偿信号DOS[2]。图1即为TCDl200D各路驱动信号的时序关系。

图2为TCD1200D驱动电路脉冲宽度与延时关系图,其中SH与F1的脉冲间隔t1,t5最小值为O,典型值为100 ns;SH脉冲上升与下降时间t2,t4最小值为O,典型值为50 ns;SH脉冲宽度t3最小值为200 ns,典型值为1 000 ns;F1,F2脉冲上升、下降时问t6,t7最小值为0,典型值为60 ns;RS脉冲宽度t8最小值为40 ns,典型值为250 ns;F1,F2与RS脉冲间隔t9。最小值为100 ns,典型值为125 ns。

2驱动电路设计与实现

2.1驱动电路设计

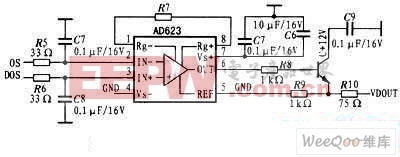

本设计采用wZE-SPXO10.00 MHz晶振作为系统标准时钟。按照TCDl200D时序要求,时钟脉冲F1,F2设为O.5 MHz,将晶振20倍分频作为F1和F2输入信号,RS的周期为1 000 ns,TCDl200D包含2 160个有效像元,有效像元前后各有64及12个哑单元,所以SH的周期应该大于等于2 236个RS周期,令SH的周期为2 240个RS周期,即2.24 ms。图3为本论文设计的TCDl200D驱动波形图,单位均为ns。

在图3中,时钟脉冲F1和F2的脉冲宽度为1 000 ns,SH的脉冲宽度为800 ns,其上升沿和下降沿与对应的时钟脉冲Fl和F2上升沿、下降沿间隔100 ns,RS的脉冲宽度为200 ns,他的下降沿与F1的上升沿间隔300 ns。可见本设计符合TCDl200D的驱动时序要求。

2.2 VHDL语言实现

Max+PlusⅡ是A1tera公司推出的一种开发设计平台,他功能强大,可以生成图形义件,文本文件和波形文件。并支持层次设计和从顶至底的设计方法,支持VHDL语言。可以编译并形成各种能够下载到各种CPLD器件的文件,还可以进行仿真以检验设计的可行性[3]。

硬件描述语言(Very high speed integerated circuitHardware Description Language,VHDL)源于美国国防部。他是用来描述集成电路的结构和功能的标准语言,设计人员无需通过门级原理图,而是针对设计目标进行功能描述,从而加快设计周期,VHDL元件的设计与工艺无关,方便工艺转换[4]。基于以上优点,本系统采用VHDL语言实现CCD驱动时序电路,下面是部分代码:

rs:process(clk)一10 MHz晶振,经分频产生RS时序

2.3 仿真结果

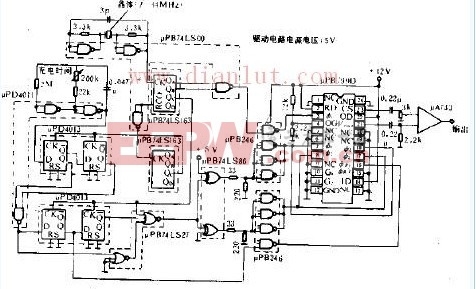

在进行了VHDL描述和编译后,就可以应用EDA软件进行驱动时序的功能仿真。功能仿真是在Max+PlusⅡ软件环境下进行的。时序仿真波形如图4所示,其中下图为上图的放大效果。CLK的频率为10 MHz,生成的时钟脉冲信号F1和F2周期为2μs,脉冲宽度为1 μs;产生的SH信号周期为2.24 ms,SH为高时脉冲宽度800ns;RS信号周期为lμs,RS为高时脉冲宽度200 ns。通过图4,可以看出设计时序符合要求。

3 结 语

本文在分析TCDl200D的工作原理和驱动信号时序要求的基础上,结合CPLD技术,采用VHDL语言,设计了一种合理的时序控制方案,通过时序仿真和实际测量,可以得出:相对于早期的驱动方式,采用CPLD技术实现CCD时序驱动电路设计简单、体积小、灵活性好;设计完成后,先通过计算机进行仿真,再实际投人使用,降低了使用风险性;实现了对CCI)器件的正确驱动。

电荷放大器相关文章:电荷放大器原理

评论