为什么QLC可能是NAND闪存的绝唱?

20 世纪 90 年代末,以 NAND 闪存为基础的固态存储得到广泛应用。从便携式设备的存储卡到台式机和笔记本电脑的存储设备,人们预言未来的数据存储将摆脱磁性存储的束缚。随着固态硬盘(SSD)在消费市场的兴起,有些人认为,用不了多久,每个人都会使用固态硬盘,而硬盘驱动器(HDD)将被淘汰出历史舞台,因为固态硬盘的每千兆字节价格和总体性能实在是太有竞争力了。

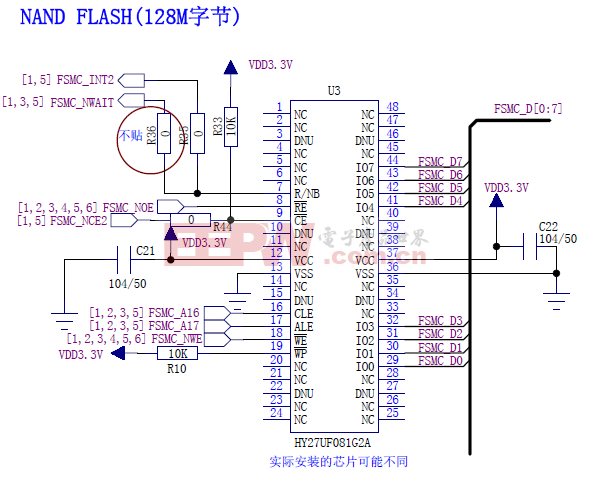

本文引用地址://www.cghlg.com/article/202407/461042.htm现在人们正在改装固态硬盘,以减少其存储空间,从而降低其性能和使用寿命。究其原因,主要是 NAND 闪存已经达到了一定的密度极限,无法再进一步扩展。改变方法包括在闪存上堆叠更多层(3D NAND),以及增加单个单元内的电压电平数量,从而增加位数。虽然这提高了存储容量,但从单层单元(SLC)到多层单元(MLC)以及今天的 TLC 和 QLC NAND 闪存的过渡却带来了严重的代价,主要表现为写入周期受限和传输速度大大降低。

浮栅概念

NAND 闪存的核心是浮栅概念,该概念最早于 20 世纪 60 年代由浮栅 MOSFET ( FGMOS ) 提出。由于 FGMOS 允许在浮栅中保留电荷,因此它推动了 EPROM、EEPROM 和闪存等非易失性半导体存储技术的发展。对于 EPROM,每个单元由一个带有浮栅和控制栅的 FET 组成。通过在控制栅上施加编程电压来诱导热载流子注入 ( HCI ),电子被注入浮栅,从而有效地打开 FET。这样就可以读出晶体管的状态并将其解释为存储的位值。

当然,只能对 EPROM 进行一次编程,然后需要通过将整个芯片暴露在紫外线下(以在氧化硅内引起电离,从而放电 FET)来擦除值。即使它允许芯片被重写数千次。为了使 EPROM 可在线重写,EEPROM 使用两个额外的晶体管改变了基本的仅 FET 结构。最初,EEPROM 使用相同的 HCI 原理来擦除单元,但后来它们改用 Fowler-Nordheim 隧穿(FNT,场电子发射的波机械形式)来擦除和写入单元,从而消除了热载流子降解 (HCD) 的破坏性影响。HCD 和 FNT 的应用都是物理损坏的主要来源,最终导致单元「泄漏」并使其变得无用。

结合电荷捕获闪存 ( CTF ),用更耐用、更强大的氮化硅材料取代原来的多晶硅浮栅,现代 EEPROM 可在磨损前支持大约一百万次读/写循环。

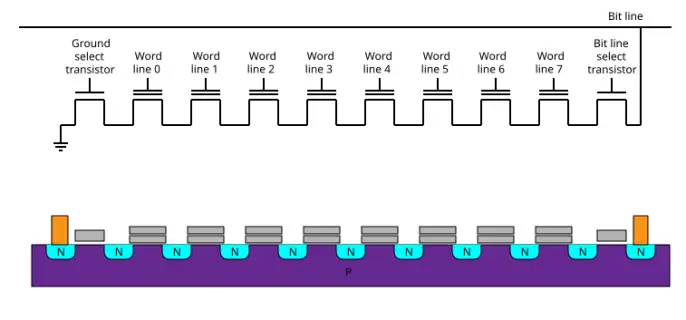

闪存是 EEPROM 的进一步发展,主要区别在于注重速度和高存储密度,以及使用 HCI 在 NOR 闪存中写入,因为这可以提供速度优势。NOR 和 NAND 闪存之间的区别在于单元的连接方式,NOR 闪存之所以这样称呼,是因为它的行为类似于 NOR 门:

NOR 闪存硅片上的布线和结构。来源:Cyferz

要写入 NOR 闪存单元(将其设置为逻辑「0」),需要将升高的电压施加到控制栅极,从而产生 HCI。要擦除单元(将其重置为逻辑「1」),需要将相反极性的大电压施加到控制栅极和源极端子,这会由于 FNT 将电子从浮栅中拉出。

然后通过将目标字线拉高来读取单元。由于所有存储 FET 都连接到地和位线,因此如果浮栅处于活动状态,这将拉低位线,从而产生逻辑「1」,反之亦然。NOR 闪存设置为允许逐位擦除和写入,尽管现代 NOR 闪存正在转向以块为单位进行擦除的模型,就像 NAND 闪存一样:

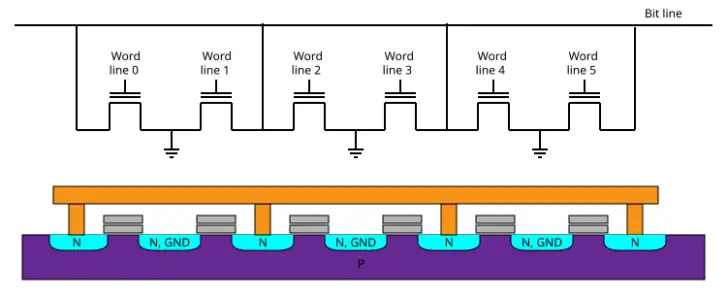

NAND 闪存硅片上的布线和结构。来源:Cyferz

NAND 闪存之所以被这样称呼,原因很容易从单元的连接方式看出,位线和地之间有多个单元串联(串)。NAND 闪存使用 FNT 进行写入和擦除单元,由于其布局,必须始终以页面(字符串集合)进行写入(设置为「0」)和读取,而擦除则在块级别(页面集合)上执行。

与 NOR 闪存和 (E)EPROM 不同,读取值比切换控制门和检查位线的电平要复杂得多。相反,必须激活目标单元上的控制门,同时对串中不需要的单元的控制门施加更高的电压 (>6V)(无论如何都会打开它们)。根据浮栅内的电荷,位线电压将达到一定水平,然后可以将其解释为某个位值。这也是 NAND 闪存能够通过依靠对浮栅电荷水平的精确测量来在每个单元中存储多个位的方式。

所有这些意味着,虽然 NOR Flash 支持随机(字节级)访问和擦除,因此支持就地执行(XiP,允许直接从 ROM 运行应用程序),但 NAND Flash 的(逐块)写入和擦除速度要快得多,再加上可能的更高密度,使得 NAND Flash 成为桌面和移动数据存储应用的首选。

扩展难题

随着对闪存每平方毫米字节数的需求不断增加,制造商已尽最大努力缩小构成 NAND 闪存芯片的晶体管和其他结构。这导致了诸如由于电子泄漏导致数据保留时间缩短以及由于结构变薄导致磨损增加等问题。通过在每个单元中存储更多位来快速轻松地增加总存储大小的方法不仅加剧了这些问题,而且还带来了巨大的复杂性。

从 NAND 闪存的耐久性等级(每个块的编程/擦除 (P/E) 周期)来看,磨损的增加显而易见,SLC NAND 闪存的 P/E 周期高达 100,000 次,MLC 低于 10,000 次,TLC 约为 1,000 次,QLC 降至数百次 P/E 周期。同时,较小的特征尺寸使 NAND 闪存更容易受到电子迁移率(例如高环境温度)引起的电子泄漏的影响。数据保留率也会随着磨损而降低,因此,对于高密度、每个单元多比特的 NAND 闪存,数据丢失的可能性越来越大。

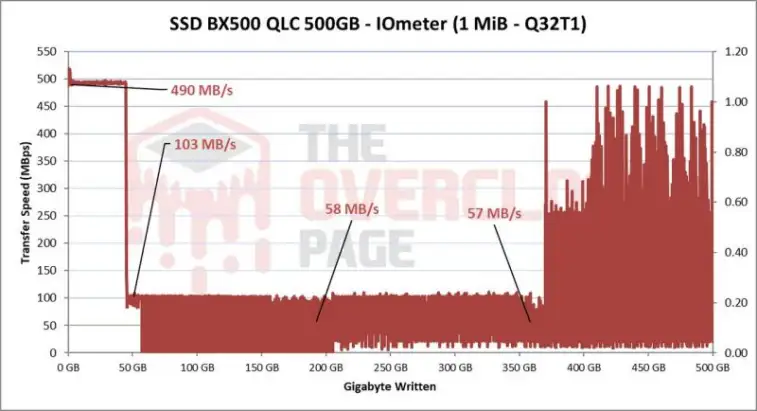

由于 QLC NAND Flash 的复杂性,每个单元有 4 位(因此有 16 个电压级别),与 TLC 尤其是 SLC 相比,写入和读取速度大幅下降。这就是为什么 QLC(和 TLC)SSD 使用伪 SLC(pSLC)缓存的原因,该缓存将 SSD 闪存的一部分分配给速度更快的 SLC 访问模式。在 Gabriel Ferraz 之前引用的教程中,通过写入超出目标 SSD(Crucial BX500)的 pSLC 缓存大小来说明这一点:

来源:Gabriel Ferraz

尽管最初写入目标 SSD 的速度接近 500 MB/s,但当 45 GB pSLC 缓存填满时,写入速度会降低到底层 Micron 3D QLC NAND 的写入速度,约为 50 MB/s。实际上,QLC NAND 闪存并不比机械 HDD 快,而且数据保留和耐用性特性更差。显然,这就是预言中的固态存储未来崩溃的临界点,因为即使是相对便宜的 NAND 闪存也还没有赶上 HDD 的性价比。

Gabriel Ferraz 对 BX500 SSD 进行的修改涉及使用 MPTools 软件重新编程其 Silicon Motion SM2259XT2 NAND 闪存控制器,该软件未提供给消费者,但已泄露到互联网上。虽然不像切换「将整个 SSD 用作 pSLC」选项那么简单,但这最终是将修改后的固件刷新到驱动器后的结果。

现在,BX500 SSD 运行在 pSLC 模式下,存储容量从 500 GB 降至 120 GB,但 P/E 评级从 QLC 模式下的额定 900 次循环上升到 pSLC 模式下的 60,000 次循环,或远超 3,000%。写入性能持续为 496 MB/s,没有 QLC 模式下的任何峰值,导致 PCMark 10 全系统驱动器测试中的得分大约翻了一番。

考虑到所有这些,很难找到一条不会让现有问题进一步恶化的 NAND 闪存技术。也许英特尔和美光不久就会推出出人意料的 3D XPoint 相变内存新方案。

评论