三星Exynos 2500芯片试产失败:3nm GAA工艺仍存缺陷

最新报道,三星的3nm GAA生产工艺存在问题,原计划搭载于Galaxy S25/S25+手机的Exynos 2500芯片在生产过程中被发现存在严重缺陷,导致良品率直接跌至0%。

本文引用地址://www.cghlg.com/article/202402/455448.htm报道详细指出,由于Exynos 2500芯片在3nm工艺下的生产质量问题,未能通过三星内部的质量检测。这不仅影响了Galaxy S25系列手机的生产计划,还导致原定于后续推出的Galaxy Watch 7的芯片组也无法如期进入量产阶段。

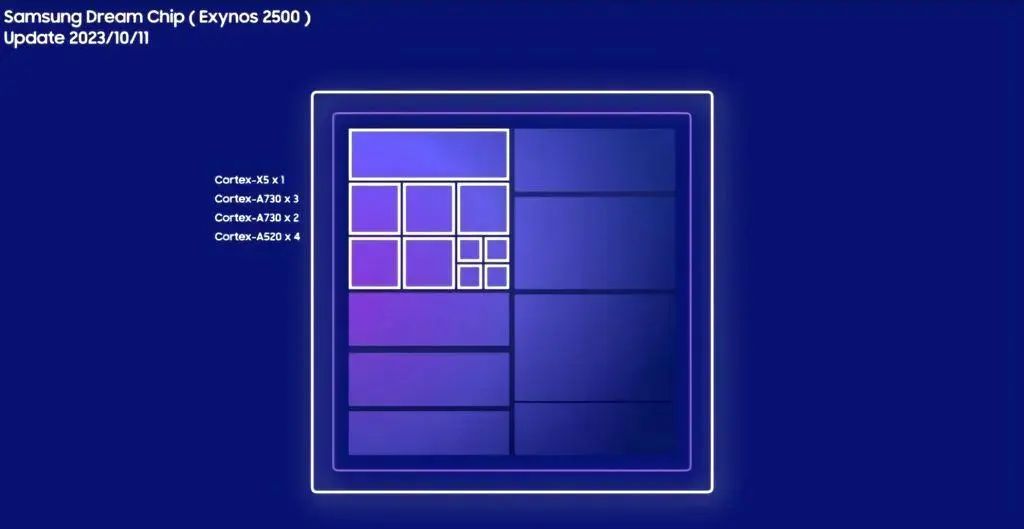

值得关注的是,Exynos 2500原计划沿用上一代的10核CPU架构,升级之处在于将采用全新的Cortex-X5以及Cortex-A730内核,相较于Exynos 2400所采用的Cortex-X4与Cortex-A720内核,性能预计将有显著提升。至于低功耗核心,新旧两代芯片都将使用相同的Cortex-A520,但具体频率尚未透露。

然而遗憾的是,Cortex-X5和Cortex-X4的时钟频率差异微乎其微,测试频率在3.20GHz和3.30GHz之间。最终,Exynos 2500的时钟频率提升可能仅为100MHz,甚至可能根本没有任何提升。

目前,由于Exynos 2500芯片的试产失败,三星已经被迫推迟了大规模生产的计划。这一事件对于三星来说无疑是一次重大的挫败,尤其是在其与台积电在半导体工艺制程领域的竞争日益激烈的情况下。目前尚不清楚三星是否有能力及时解决这个良率问题。

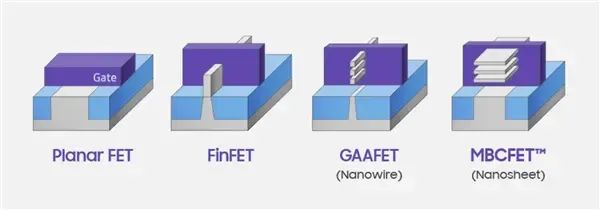

事实上,三星的3nm工艺技术在业界被视为一项重大突破。相比台积电在2nm工艺制程上才会转向GAA晶体管的路线策略,三星在第一代3nm工艺上就采用了GAA晶体管技术,而且是MBCFET多桥通道场效应晶体管,被称为SF3E,也就是3GAE工艺。

这种技术采用了更宽通的纳米片,与采用窄通道纳米线的GAA技术相比能提供更高的性能和能耗比。此外,GAA的设计灵活性对设计技术协同优化(DTCO)非常有利,有助于实现更好的PPA优势。

据称,与三星5nm工艺相比,第一代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而未来第二代3nm工艺则使功耗降低50%,性能提升30%,芯片面积减少35%。

然而,尽管技术上取得了一定的突破,但三星在试产阶段却遭遇了良品率的问题。这不仅让业界对其3nm工艺技术的成熟度产生了质疑,也让人们对三星在半导体领域的竞争前景感到担忧。毕竟,对于一家以技术为驱动的公司来说,芯片良品率的问题可能会对其市场份额和声誉造成重大影响。

三星在芯片制程方面的挫折,不仅影响了其晶圆代工业务,也对其存储器和手机业务造成了负面影响 —— 三星在DRAM制程方面也遇到了瓶颈,拿着EUV设备却干不过美光的DUV设备,密度和成本都处于劣势。

反观台积电,其在先进制程的步伐非常稳健。2022年12月29日,台积电布3nm芯片即日起开始量产;2023年以来,基于台积电3nm制程工艺的芯片已陆续发布,如联发科天玑9400芯片、苹果A17 Pro等。

台积电明年的3nm NTO芯片设计定案(New Tape-Outs,NTOs)数量激增,除了传统客户联发科、AMD、英伟达、英特尔、高通外,特斯拉也确认加入N3P客户名单,预计将以此生产次世代FSD智驾芯片。

三星3nm制程工艺的芯片在量产商用上仍遥遥无期,这意味着该领域将在一段时期内被台积电垄断,其中的利润不用多说:台积电方面表示2023年第四季度的营收得益于3nm工艺产量的持续强劲增长,并且仅仅两个季度就为台积电贡献了29.43亿美元。

虽然台积电3nm工艺是基于旧技术路线,但根据台积电的数据,与5nm工艺相比,N3E可以在相同频率下降低32%的功耗,或者在相同功耗下提高18%的性能;而相较于N3E,N3P则可以在相同功耗下提高5%的性能,或者在相同频率下降低5%~10%的功耗,还可以将晶体管密度提高4%,达到1.7倍于5nm工艺的水平。

评论