高压电解电容波峰焊放电击穿板上芯片的机理研究及对策

王大波,施清清,李会超,宗 岩 (珠海格力电器股份有限公司,广东 珠海 519000)

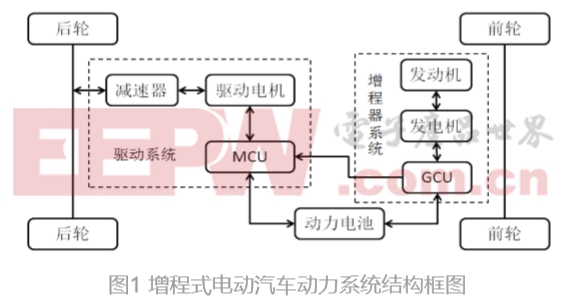

摘 要:芯片失效作为困扰电子行业的难题,失效机理复杂,对于因生产现场环境造成的过电、静电失效,环 节无法锁定。通过对高压电解电容带电插装对印制电路板上芯片损伤分析,确定主板过波峰焊时锡面连锡短路 导致高压电解电容放电击穿芯片的失效机理,并制定管控对策,有效降低芯片失效不良。

0 引言

随着电子技术的发展,小型化、集成化的芯片被应 用于各个领域,如何保证自身可靠性及产品质量成为芯 片厂商不断深入研究的热点。但芯片因生产环境、使用 环境苛刻,失效情况时有发生[1]。目前业界已经识别到 的失效原因分两大类:①芯片本身制造缺陷;②生产 现场不规范操作导致失效。业内常用的失效分析方法 包括:芯片开封、X-Ray无损探伤、SEM扫描电镜、 EMMI侦测等。此类分析方法对于芯片制造缺陷,如晶 元异常、金线绑定异常等能直观判断失效环节,但是对 于因生产现场环境造成的EOS(过电应力)、ESD(静 电放电)却难以锁定失效点,给生产、产品质量改善带 来不便。

电解电容因容量大,广泛应用于输出滤波电路中, 起储能和滤波作用[2-3]。高压电解电容因其制造工艺及 电子特性,在插装前会残留部分电压,而残留电压对于 电路板上半导体器件的影响一直被行业内电路设计者所 忽略。学者针对高压电解电容残留电压对芯片失效进行深入研究,并做了充分试验验证。结果表明高压电解电 容未放电即插装,在过波峰焊时会通过锡面将残留电压 作用于芯片上,致使芯片失效。同时,学者通过大量数 据验证,通过改进电路布局或过板方向,有效解决了因 高压电解电容未放电导致的芯片失效,降低产品不良 率,提高产品可靠性[4-5]。

1 案例分析

1.1 背景

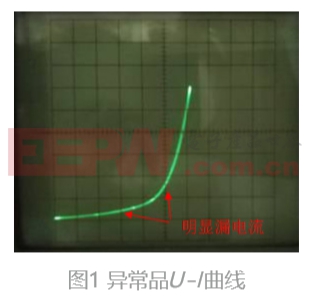

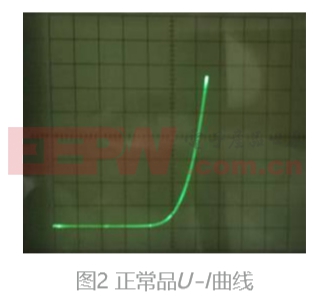

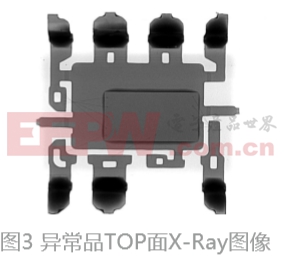

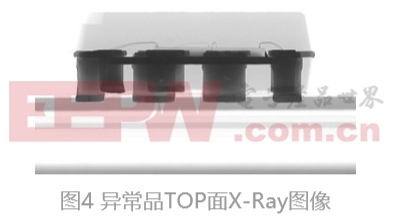

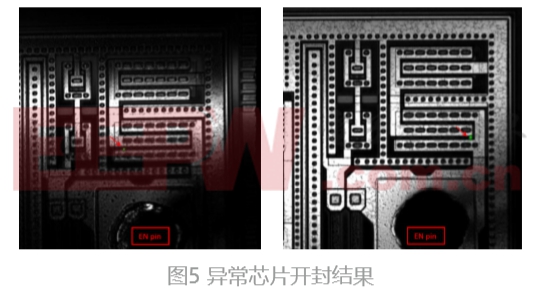

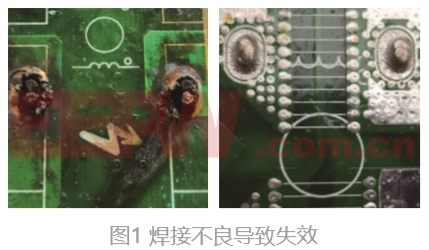

控制器车间生产某两款主板,某厂家开关电源芯 片零星下线,批次不集中,失效外在表现为芯片的1脚 (使能脚)与5脚(地脚)之间阻抗值异常,正常品阻 抗为M欧级别,失效品阻抗为K欧级别。对正常、异常 芯片分别测试U-I曲线,如图1、图2所示,表明芯片失 效,有漏电流。图3、图4为异常芯片X-Ray图像,结果 表明芯片内部结构无明显异常。经厂家对芯片开封确 认,如图5所示,确认芯片失效模式为过电损伤。

1.2 分析过程

取库存开关电源芯片,对 PIN1(EN/UV)脚与 PIN5(S)脚施加15 V直流电压,测试阻值,试验后芯 片1~5脚阻抗在10 kΩ左右,与下线异常品阻抗一致, 测试U-I曲线与下线品一致,存在明显漏电。经对芯片 开封确认,芯片属过电失效。

对生产线及员工的静电防护、在线测试设备进行排查,未发现异常。为锁定失效环节,对未上线芯片全检 1~5脚阻抗,无异常后进入下一生产流程。最终锁定失 效环节发生在主板进入波峰焊后与出波峰焊间,进一步 检查波峰焊设备接地状态及防静电检查,无异常。初步 分析为高温导致芯片失效。因芯片为SMT贴装,对比回 流焊、波峰焊温度及过板时间,回流焊环境更为恶劣, 但未出现异常。同步安排芯片高温、低温、冷热冲击、 高温潮态试验均未发现异常,锁定失效发生在波峰焊浸 锡环节。

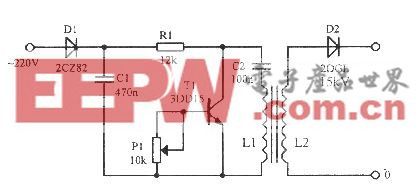

对开关电源芯片电路分析,电路中有450 V/22 μF的 电解电容,初步锁定过电源为电解电容放电异常。经验 证,使用直流电源对主板上电解电容充15 V的直流电后 对开关电源芯片1-5脚进行放电,芯片失效,与下线样 品现象一致。查询该芯片技术参数,PIN1脚(EN/UV) 工作的最大额定电压为9 V,高于9 V有过电击穿隐患。 随机抽取350个未上线使用的电解电容测试残余电压, 有3个电压高于10 V,理论上高压电解电容残余电压在 未放电即插装使用存在击穿芯片隐患。

2 实验验证

2.1 验证条件及结果

1.同编码电容及下线主板;

2.残余电压:30 V;

3.验证数量:30 PCS;

4.验证结果:未复现。

2.2 原因分析

通过对生产过程及波峰焊内部构造分析,确认未复 现原因有以下3点:

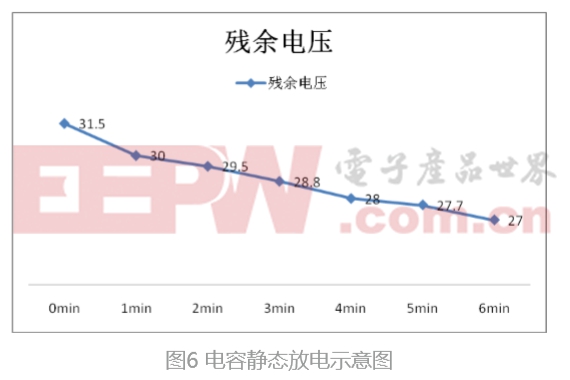

1)电解电容充电后会静态放电,下线主板由波 峰焊入口到锡炉位置需5 min,同步做电容静态放电试验,如图6所示,表明电容残余电压随时间递减。

2)电解电容插装后由插件段至波峰焊锡炉过程 中,因链爪不平稳电容在晃动过程中引脚会碰到焊点过 孔沉铜,经由印制线路板回路中耗能器件,加速电容 放电。经验证,电容充电后,人为晃动电容会加速放 电。同步对充电后电容在波峰焊内部不同阶段残余电压 测量,浸锡前残余电压相差较大,高可至20 V,低可至 5 V以下,表明电容带电插装后其放电过程属随机过 程,存在偶发性。

3)高压电解电容放电击穿芯片发生在主板浸锡过 程中,因该芯片为SMT贴装,需满足电容引脚和芯片1 脚测试点同时接触锡面方可实现放电。锡炉的锡面为锯 齿状斜坡面,波峰高度有差异。同时,若电容双引脚浸 锡则放电给锡面而不会给芯片。

结合以上三点,高压电解电容放电击穿芯片需空间 与时间上同时满足要求,为概率性事件,此为该芯片零 星下线原因。

3 失效机理分析

3.1 失效机理

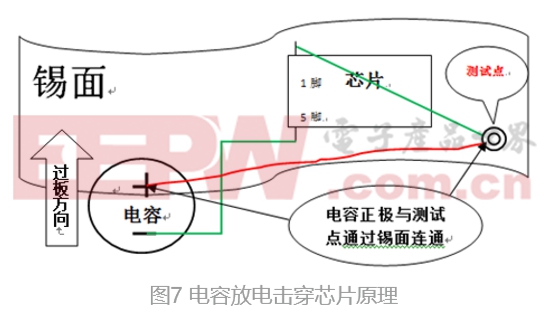

对主板电路及过板方向进行分析,电容负极与开关 电源芯片5脚共地,芯片1脚与过孔测试点共线路。当测 试点、电容正极同时处于锡面时,电容的正极与测试点 通过锡面连通,即此时电容正极与芯片1脚连通形成回 路,相当于电容储存电量直接作用于开关电源芯片,致 使芯片失效,失效机理如图7所示。

用导线将电容的正极与测试点短接,模拟过锡炉情 形,短接导线模拟测试点与电容正极同时浸锡锡面。 电容充电后插装,测试芯片1~5脚阻抗,阻抗异常,与 下线现象一致。同步增加电容带电插装验证,故障可 复现。

3.2 失效模式确认

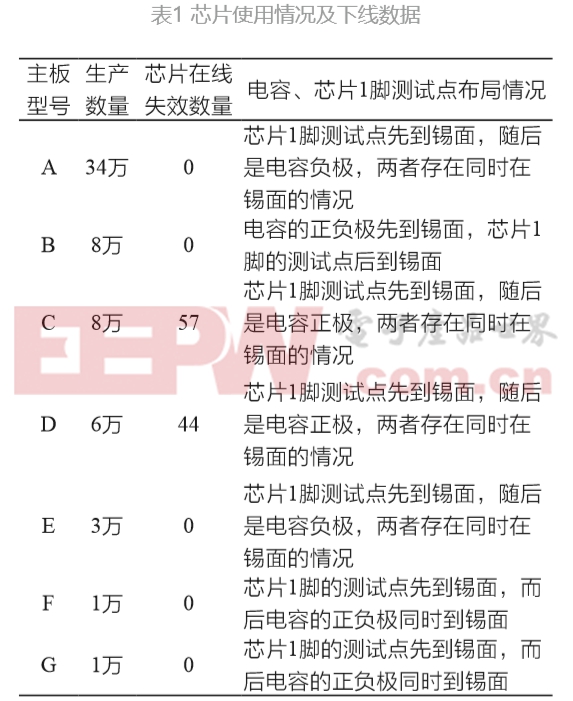

此开关电源芯片共使用在7款PCB上,统计18个月 生产数量及芯片下线数量如表1所示。

从上表可以得出,迄今此开关电源芯片所用的板, 只有C、D两款主板有下线,针对此主板上的开关电源 芯片、电容、测试点、过板方向等布局展开研究。

B主板从过板方向看,电容先于芯片1脚测试点浸 锡,电容过锡炉时电容正负极先接触锡面,测试点还未 接触锡面前电容已放电,因此没有电容放电给芯片的 条件。

F、G 两款主板芯片1脚的测试点先接触锡面,而后 电容正负极引脚同时浸锡,三者有共同处于锡面的时 间,但当电容的正负极同时浸锡时,电容即放电,不会 再通过测试点回路放电给芯片。

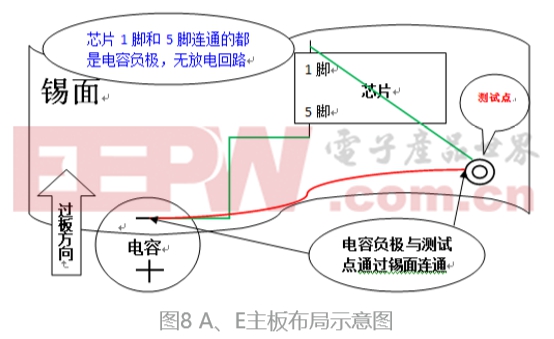

A、E两款主板从过板方向看,芯片1脚测试点先过 锡炉,存在电容、测试点同时处于锡面的条件,但是此 主板的电容是负极先接触锡面,即存在电容负极、测试 点同时处于锡面的情况。此时电容负极通过锡面与测试 点连通,测试点与芯片1脚连通,即电容负极与芯片1脚 连通,而电容的负极与芯片的5脚是连通的,此时相当 于电容的负极同时与芯片的1脚和5脚连通,而此时电容 的正极在锡面以外,显然无放电回路,如图8所示。当 电容的正极进入锡面以后,电容的正极与负极通过锡面 连通,电容的电会直接通过锡炉释放。

排查C、D两款主板历史在线失效数据时,了解到 此两款主板的最初生产的阶段此开关电源芯片无在线失 效案例,进一步调查发现,此两款主板 进行过三次版 本升级,更改后开始出现芯片在线失效,对比几次更改 情况,第一次更改调整了电容、芯片、测试点的布局, 改变了波峰焊阶段电容放电回路,满足电容对芯片放电 的条件,此点更改后一直延续到后面的版本,因此第一 次更改后的版本都出现过此芯片的零星下线。

为验证以上分析的准确性,将C、D两款主板改变 过板方向,从而破坏了电容放电给芯片的放电回路,累计验证数据超过3 W,开关电源芯片无一在线失效案 例,进一步佐证了分析的准确性。

4 结论与对策

4.1 研究结论 芯片生产线失效的原因为同主板的高压电解电容存 在放电不彻底的情况,当主板经过锡面时,电容的正极 与芯片1脚的测试点同时处在锡面,而测试点是与芯片1 脚连通的,同时电容的负极与芯片的5脚连通,即相当 于电容的正负极分别加在芯片的1脚和5脚,从而将参与 电压释放在上,导致芯片过电失效,原理如图7所示。

对于DIP封装的芯片,无需依靠测试点,芯片的引 脚直接与锡面接触,此种情况下,需考虑芯片上高压电 解电容在主板上的空间布局,同时要考虑锡面的宽度。 芯片过电损伤后,其在厂内并不以某种失效形式表现, 但长期运行影响芯片及成品可靠性。

4.2 解决对策

为减少因高压电解电容未放电插装导致的芯片失 效,可选择以下方案进行解决:

1)PCBA的空间布局满足电解电容两正负引脚的连 线垂直波峰焊过板方向,既确保电容的正负引脚同时进 入锡面,将可能存储的电放给锡面。

2)贴片封装的芯片考虑将其测试点布控在远离高 压电解电容的位置,具体是平行过板方向的距离大于波 峰焊锡炉锡面的距离,DIP封装芯片考虑芯片本身远离 高压电解电容的位置,具体是平行过板方向的距离大于 波峰焊锡炉锡面的距离,同时确保与芯片引脚连通的电 容引脚先到达锡面。

参考文献:

[1] 袁宝玉, 侯旎璐, 李进. 电压检测芯片失效分析 [J]. 电子产品可 靠性与环境试验, 2017, 35(4): 49-56.

[2] 黄伟华, 陶书梓. 从铝电解电容典型失效案例分析看品质提升 [J]. 光源与照明, 2013(3): 19-24.

[3] 潘启军, 黄垂兵, 邓晨. 电解电容与薄膜电容对比分析 [J].海军 工程大学学报, 2014,26(2): 5-9.

[4] 熊克勇, 项永金, 崔斌, 等. 变频空调开关电源电路开关芯片 炸失效分析与研究 [J]. 电子产品世界, 2016(2): 40-42.

[5] 周慧德. 开关电源中铝电解电容可靠性的研究 [D], 哈尔滨, 哈尔滨工业大学, 2010.

本文来源于科技期刊必威娱乐平台 2020年第03期第66页,欢迎您写论文时引用,并注明出处。

评论