金手套 ADC 锦标赛――SAR 迎战

一边是当前流行的SAR ADC,另一边是相对较新的模数转换技术∑△ADC,二者比拼的结果会是如何呢?

本文引用地址://www.cghlg.com/article/201809/388834.htm我们要进行七轮角逐,在这七轮中将分别就以下分类项目打分:

1 转换准确性

2 转换速度

3 攻击线性

4 高低压侧转换准确性

5 差动非线性

6 积分非线性

7 量化误差

人们已经对两种技术的比拼等待了很长时间。SAR ADC 和它的新近挑战技术终于能够进行一对一的比拼了。谁能最终获胜呢?SAR ADC 的特点是体形较大(采样和保持电路),速度较快,决定性较弱;而∑△ADC 则属于轻量级选手,其采用了集成电路以及科学的方法和准确的思考进程。

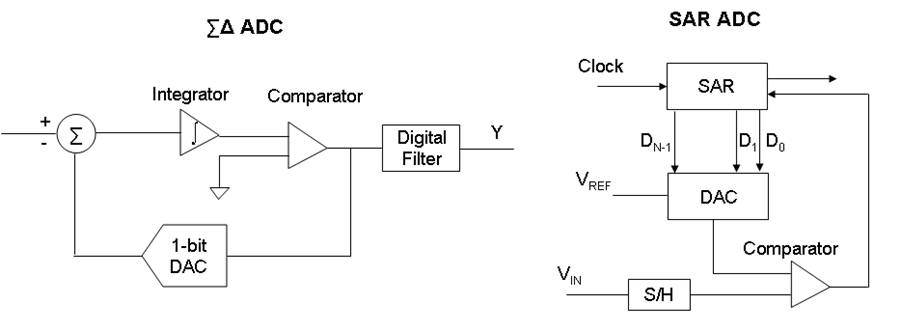

图 1:∑△ 和 SAR 拓扑

图中文字:integrator:积分器

comparator:比较器

digital filter:数字滤波器

clock:时钟

第一轮:转换准确性

准确性是由增益误差和非线性决定的。我们在这一轮在讨论的是增益误差,非线性问题将在第五轮和第六轮比拼中讨论。

增益误差有两种。刻度 (scale) 信号误差是由参照差异以及输入和 ADC 之间增益通道的差异造成的,误差的大小与信号强弱相关。偏置误差是由输入放大器中的输入器件以及 ADC 积分电路/比较器中使用的运算放大器造成的。

我们在图 1 中可看到∑△的调制器(积分器、比较器和 1 位 DAC)和数字滤波器。∑△ADC 可在其前端包含可选的增益放大器。改变放大器的增益会改变输入采样电容的大小。由于采样电容存在差异,因此增益不会是绝对精确的,需要 ADC 校准。为了纠正偏置和增益误差,我们要根据零转换、正满刻度转换和负满刻度转换结果获得校准因数。

另一方面,SAR ADC 的转换准确性取决于电压参照、内部 DAC 和比较器。ADC 的内部 DAC 和比较器的准确性应和整体系统一样,任何的不准确都会导致线性误差,而这是校准所不能解决的。

在第一轮中,∑△ADC因其自身的单调性而胜出。

第二轮:转换速度

∑△转换器需要 2n 个采样来完成转换,因此转换速度取决于转换器的分辨率。分辨率越高,需要的转换时间就越长。数字音频设备通常使用的传统∑△转换器带宽约 22kHz。近期,带宽达 1MHz ~ 2MHz、分辨率达 12 ~ 20 位的∑△转换器已经上市,这些转换器通常包含四级(乃至更高)∑△调制器,而且支持多位反馈 DAC。

在SAR ADC 转换周期开始时,DAC 设为半刻度,并对待测电压和 DAC 输出进行比较。DAC 在每一步进中都进行更新,选择下一位并进行比较。我们通过二进制搜索(“逐次逼近”)来发现输入电压的数字形式。

SAR ADC在第二轮中因其转换算法实际速度较高而胜出。

第三轮:攻击线性

差动非线性 (DNL) 和积分非线性 (INL) 这两种形式的非线性都取决于拓扑和转换器的构造。DNL 和 INL 误差不能像增益和偏置误差一样通过校准解决。

∑△ADC 的准确性取决于积分电路/比较器中运算放大器的稳定性。如果调制器切换太快,而运算放大器不能保持同步,则会出现非线性问题。

不管分辨率达到多少位,∑△ADC 本身都是单调性的。其性能是固定的,并不取决于具体的组件值或组件匹配。

就 SAR ADC 而言,线性误差是由内部 DAC 和比较器的准确性不高造成的。线性误差是 SAR 设计的副效应。

第三轮的胜出者是∑△ADC。

第四轮:高低压侧的转换准确性

∑△转换器提高了特定输出代码的非线性,这取决于抽取器中所用的 FIR 滤波器。这种非线性主要出现在刻度端点上。端点非线性对持续数据流(如数字音频)不构成问题,但系统如果需要轨到轨线性检测,则不应使用 ∑△转换器。

SAR ADC 不会出现较大的∑△转换器高低压侧端点不准确性问题。其端点准确性取决于内部 DAC 和比较器的轨到轨跟踪(电压合规)。

SAR ADC在第四轮在因其高低压侧的准确度较高而胜出。

第五轮:差动非线性

差动非线性误差是指实际步进和 1 LSB 理想值之间的差异。因此,如果步长或高刚好为 1 LSB,那么差动非线性误差就为零。如果 DNL 超过 1 LSB,则转换器可能是非单片的,这就意味着输出强度会下降,而输入强度上升。在 ADC 中,也可能出现丢失代码的问题,如一个或多个 2n 二进制代码无法输出。

不管分辨率达到多少位,∑△ADC本身都是单调性的。其性能是固定的,并不取决于具体的组件值或组件匹配。

SAR ADC 本身不是单调性的,其性能取决于具体的组件值或组件匹配。

第五轮的胜出者是∑△ADC。

第六轮:积分非线性

积分非线性误差体现为实际转换函数与直线之间的偏差。直线可以是可尽可能降低偏差的最佳直线,也可以是增益和偏置误差取消后在转换函数端点之间所画的直线。对 ADC 而言,偏差是两个步进之差,积分非线性顾名思义就是指从下至特定步进的差动非线性之和,其决定着步进的积分非线性值。

第六轮的胜出者是∑△ADC。其设计并不取决于具体的组件匹配或组件值。SAR ADC则需要高度准确的DAC和比较器。

第七轮:量化误差

量化误差是由 ADC 有限的分辨率造成的,也是各种类型 ADC 所无法避免的缺陷。它是 ADC 模拟输入电压和输出数字化值之间的化整误差。噪声就是非线性的,并从属于信号。

∑△转换器不需要抗混滤波器,由于采样率大大高于有效带宽,因此模拟输入处会出现骤降。过采样会平衡掉模拟输入处的任何系统噪声。∑△转换器的速度较慢,但分辨率较高。

SAR ADC的主要优势在于低功耗、高分辨率和准确性。在SAR ADC中,提高分辨率会增加更为准确的内部组件成本。

尽管∑△ADC 在多轮比拼中获胜,但评委还是认为二者基本打平。两种转换器在特定应用中的表现很好,因此必须根据量化信号、转换速度、转换准确性和价格来选择∑△或SAR ADC。二者都有其用武之地。

让我们从锦标赛的比拼中返回到现实的模拟领域。显而易见,在消费、汽车、医疗、到工业等各种应用中,必须检测、放大、调节和转换各种感应器采集的模拟信号,从而实现在数字领域中对其加以处理。SAR和DelSig 各有优缺点,设计人员需根据不同的具体应用要求加以选择。毫无疑问,这两种转换器在不同领域都能发挥出各自的效用,而赛普拉斯半导体公司 PSoC 产品近期提供的可编程模拟系统带来了一款灵活的平台,设计人员可用其来构建多个 SAR、DelSig,甚至同时构建SAR和DelSig。

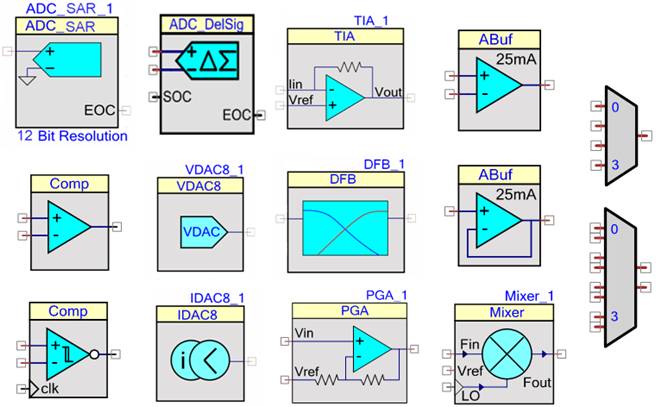

我们从图 # 看出,软件开发工具 PSoC Creator 组件库——包括能在独特软硬件协同设计环境中配置 PSoC 器件的图形设计编辑器在内的集成开发环境 (IDE)——中提供了模拟符号。模拟可编程系统创建标准和高级模拟信号处理块的专用组合。这些块彼此互联,可提供高度的设计灵活性和 IP 安全性。PSoC Creator 软件程序提供了用户友好型界面,可配置 GPIO 和多种模拟资源之间的模拟连接,也能配置模拟资源彼此之间的连接,从而帮助设计人员构建自己的组件,如一般包括 DAC、比较器和数字逻辑的 SAR ADC(图 #)。

可编程模拟不仅能实现可在最后时刻进行方案调整的灵活开发,同时还提供了一个适当的平台。无论金手套锦标赛中的胜负如何,设计人员均能借助该平台进行各种尝试并操控不同领域的各种分离式模拟组件,进而构建最佳的系统。

评论