VHDL编码中面积优化探讨

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。这种用语言描述硬件电路的方式,容易修改和保存,且具有很强的行为描述能力,所以在电路设计中得到了广泛应用。利用VHDL语言对PLD开发,面积(Area)是一个很重要的指标。通过“面积”优化可以使用规模更小的可编程逻辑芯片,从而降低系统成本;改善电路性能,降低器件功耗;为以后的技术升级留下更多的可编程资源,方便添加产品的功能。

VHDL包含的语句非常丰富,不同的描述可以实现同样的逻辑功能。但应注意,实现同样功能的不同描述,可能在综合出的电路规模上存在差异,也就是说,对资源的利用率有所不同。本文就有关VHDL编码方面的面积优化问题进行讨论。

2 常见问题

2.1 避免引入不必要的寄存器元件

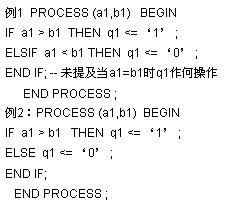

在描述组合逻辑电路时,应使用完整的条件语句结构。因为不完整条件语句的使用会引入不必要的寄存器元件,既浪费逻辑资源,又降低电路的工作速度,影响电路的可靠性[1]。例如用IF条件语句设计一个纯组合电路的比较器,比较以下两例:

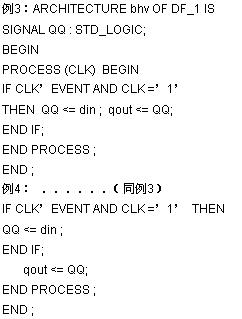

信号可以作为设计实体中并行语句模块间的信息交流通道,是具有全局性特征的数值容器。在时序电路设计中,为了在设计更大的电路时使用由此引入的时序电路的信号,常在电路内部定义节点信号。通过信号完成进程之间的通信,从而保证结构体中多个进程能够并行同步运行。寄存器描述中有节点信号时,不同的描述会产生不同的综合结果。如以下两例:

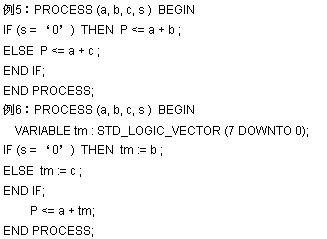

在设计数字系统时常常需要反复地调用一个同样结构的模块,这类模块往往是算术模块。如例5中两个加法器是在s不同取值时分别使用的,且输入a一直接入加法器。略作修改,如例6,可以只用一个加法器完成同样功能,从而有效地减小使用面积。

CASE语句描述的程序可读性较好,因为它把条件中所有可能出现的情况全部列出来了,可执行条件一目了然,且条件句的次序并不重要。故而是常用的条件语句之一。因为它的执行过程更接近于并行方式,一般地,综合后,对于相同的逻辑功能CASE语句比IF语句(顺序条件语句)的描述耗用更多的硬件资源[1]。

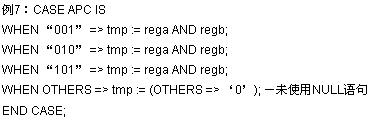

另外,Max+plusⅡ有时对NULL会出现擅自加入锁存器的情况,在用CASE语句描述组合逻辑电路时,应尽量避免使用NULL来表示未用条件下的操作行为,改用确定操作,如例7。

因为变量值是立即获得的,如果先写后读就会产生长的组合逻辑和锁存器。因此,在编写代码时,对变量要先读后写,如例8。

就综合而言,简单的比较运算符(=和/=)在实现硬件结构时,比排序操作符(>、>=、、=)构成的电路芯片资源利用率要高。因此,如有可能,应尽量用比较运算府代替排序操作符。

2.7 尽量采用可计算型下标名

下标名用于指示数组型变量或信号的某一元素。如果下标名是一个可计算的值,则此操作数可很容易地进行综合。否则,只能在特定的情况下综合,且耗费资源较大。所以,在进行电路设计时尽量采用可计算型下标名,以提高资源利用率。

3 结束语

功能强大的EDA开发软件和专业的综合工具的不断发展,使应用VHDL进行PLD设计变得更简单、更快捷。但决不能忽视VHDL语言的使用。随着所设计电路规模的增大,对有限的芯片资源的利用率问题就显得尤其重要。在不影响速度要求前提下,应尽可能地进行面积优化。适当地进行编码是优化设计的重要保障,对高质量、高效率地完成VHDL是十分有意的。

参考文献:

[1] 潘松,黄继业.EDA技术实用教程.北京:科学出版社,2002

[2] 赵刚 等.EDA技术简明教程.成都:四川大学出版社,2004

[3] 林瑶,使用VHDL语言中几个常见问题的探讨,微计算机信息:2004年,20卷,9期,136~137页

创新点:寄存器描述中有节点信号时,根据由节点信号向端口赋值语句在程序中的不同位置,综合的结果存在差异:此语句在IF条件语句之内时寄存器占用的逻辑资源比它在IF条件语句之外时多一倍。

评论