可穿戴设备和物联网的电路保护连接

电路保护技术和电路板布局策略有助于提高安全性、可靠性和连通性。可穿戴技术存在一个不可能出现在物联网新闻标题中 的弱点:人体在移动时产生静电。静电可能损坏支撑物联网 应用的敏感电子设备。

为了理解这个问题,我们从人体放电模型(H B M)开 始,应用于描述集成电路对静电放电(ESD)破坏的敏感性。 使用最普遍的H B M 概念是军用标准M I L - ST D - 8 8 3 、 方法3015.8、静电放电灵敏度分类中定义的试验模型。相似的 国际HBM标准是JEDEC JS-001。无论在JEDEC JS-001还是在 MIL-STD-883中,都用100pF电容器和1.5kΩ放电电阻器模拟 带电人体。测试中,电容器在250 V到8 kV的电压范围内完全 充电,然后通过与受试器件串联的1.5kΩ电阻器放电。

由于可穿戴设备设计为可以贴身使用,它们持续受到 因为与用户近距离相互作用而产生的静电冲击。如果没有适 当的保护,可穿戴设备的传感器电路、电池充电接口、按钮 或数据输入/输出端口有可能被与HBM试验中产生的相似的 程度静电放电(ESD)损坏。一旦可穿戴设备失效,整个网络 的功能和可靠性也会受到影响。

先进电路保护技术和电路板布局策略能保护可穿戴设 备及其使用者。尽早在设计过程中运用这些建议将帮助电路 设计者们提高其可穿戴技术设计的性能、安全性和可靠性, 并有助于构建更加可靠的物联网。

1 封装尺寸虽小,但ESD保护作用不小

可穿戴设备电路保护的一个设计挑战是可穿戴设备的 尺寸越来越小。过去,需要大结构二极管和大封装尺寸(如

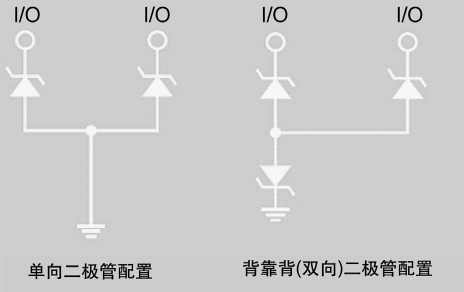

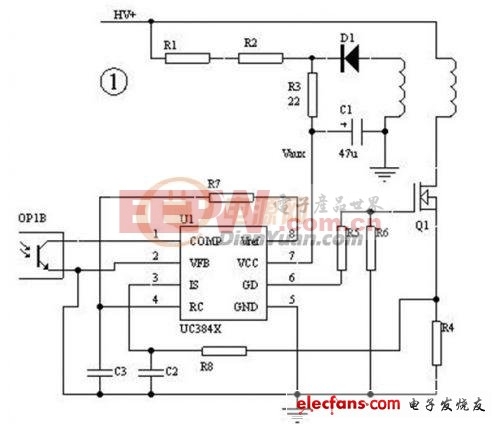

图1 TVS二极管两种结构

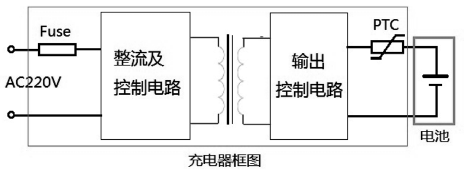

图2 IEC 61000-4-2评级

设计人员应尽可能选择单向二极管配置,因为它们在 负电压ESD冲击事件中的表现更好。负电压ESD冲击期间, 钳位电压将基于二极管的正向偏压(一般小于1.0 V)。反之, 双向二极管配置在负电压冲击期间提供的钳位电压基于反向 击穿电压,比单向二极管的正向偏压高。因此,单向配置能 大大减小负电压冲击期间对系统产生的压力。

合理确定二极管位置。大部分可穿戴设计不需要在每 个集成电路引脚上都使用板级T VS二极管。相反,设计人员应该确定哪些引脚暴露在可能发生用户可能产生ESD事件的。如果用户能接触通讯/控制线路,这可能成为ESD进入 集成电路的一个途径。倾向于存在这种途径的典型电路包 括USB、按钮/开关控制和其他数据总线。由于添加这些分 立器件设备需要占用电路板空间,因此需要能装入0201或

01005封装的器件。对某些可穿戴应用来说,可采用节省空 间的多通道阵列。无论采用什么封装类型,ESD抑制器的位 置要尽量靠近ESD源。比如,USB端口的保护应靠近USB连 接器。

缩短走线长度。走线布线在针对集成电路引脚的TVS二 极管保护设计中非常重要。与雷电瞬态不同,ESD不会长时 间释放出大量电流。处理ESD时,一定要尽快把电荷从受保 护的电路转移到ESD参考点。

首要因素是从信号线到ESD器件和从ESD器件到地的走 线长度,而非地的走线宽度。为了限制寄生电感,走线长度 应该越短越好。寄生电感会导致感应过压,这是一种短促 的电压尖峰,如果桩线够长的话,这个电压尖峰可能达到数 百伏特。近期的封装技术进步包括能直接装在数据车道上的µDFN轮廓,这样桩线就不再需要了。

理解人体放电模型(HBM)、机器放电模型(MM)和带电 设备模型(CDM)的定义。除了HBM模型之外,MM和CDM 也是描述运行便携设备或可穿戴设备的集成电路ESD耐受能 力的试验模型。不少半导体厂家认为MM模型已经过时。人 们倾向于在坚固性和产生的失效模式上跟踪HBM,尽管有 些厂家仍在使用它。CDM是HBM的另一个替代模型。与模 拟人与集成电路之间的相互影响不同,CDM模拟集成电路 滑向走向或管子,然后触及接地表面。按CDM分类的器件 在指定电压水平上接触电荷,然后测试存活率。如果器件仍 然功能正常,就在下一个电压水平上继续测试它,直到它失 效。CDM由JEDEC在JESD22-C101E中标准化。

包括处理器、内存和ASIC在内的芯片都会用这三个模 型中的一种或几种来描述。半导体供应商在制造期间使用这 些模型保证电路的健壮性。对于供应商来说,当前趋势是降 低电压测试水平,因为这样能节省晶片空间,也因为大部分 供应商遵守严格的内部ESD政策。

严格的ESD政策通过运行较低的片上ESD保护,能使供 应商受益,电路设计人员还是以对应用级ESD十分敏感的芯 片,决不允许因为现场ESD或用户致ESD而失效。为了保护 高度敏感的集成电路,设计人员选择的保护器件不仅要能防止增强的静电应力,还要能提供足够低的钳位电压。

评论