HPI接口在TI DSP中的应用及常见问题分析

5. HPI操作流程

主机对HPI的一次总线访问周期为分三个阶段:主机发起访问,HPI响应,主机结束访问周期。

A. 主机发起访问:即对HPI寄存器的读,或者写命令。主机送出的硬件信号为HSTROBE(由HCS, HDS1/2产生),HR/W,HCNTL0/1,HWIL,以及HD[0:n].HPI在HSTROBE的下降沿采样控制信号HR/W,HCNTL0/1,HWIL判断主机的操作命令。

B. HPI响应:HPI在HSTROBE的下降沿采样控制信号,根据控制信号做出相应的响应。如果是写(HR/W为低)命令,则在HSTROBE的上升沿将数据线上的信号锁存到HCNTL0/1和HWIL指向的寄存器。如果是读命令(HR/W为高),如果是读HPIC,或者HPIA寄存器,HPI将寄存器的值直接送到数据总线上;如果读HPID,HPI先将HRDY置为忙状态,HPI DMA将数据从HPIA指向的内存单元读到HPID,再送到数据线上,并清除HRDY忙状态,在读HPID后半字时,数据从寄存器直接送到数据总线上,不会出现HRDY信号忙状态。

C. 主机结束访问周期:对于写操作,主机将数据送出后,只要满足芯片手册中HPI对HCS的最小宽度要求,即可结束访问周期。对于读HPID操作,要等HRDY信号由忙变为不忙,主机才能结束访问周期。两次连续的HPI操作的间隔,在芯片手册的HPI时序参数表里有要求,最小间隔为两个HPI功能模块时钟周期。

6. HPI常见故障案例分析

在HPI应用调试过程中,常遇到的问题分为:写数据不成功,读数据不正确,HRDY常高。这些问题通常都是由于时序不正确造成的,下面结合实际应用当中的案例进行分析。

6.1 写数据不成功

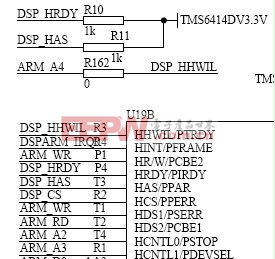

案例的硬件连接如下:

首先关注核心信号HSTROBE 由DSP_CS,ARM_WR(HDS1),ARM_RD(HDS2)产生,从下面时序图可以看出ARM_WR的下降沿是最后产生的,所以写操作时HSTROBE 的下降沿反应的是ARM_WR 的下降沿。

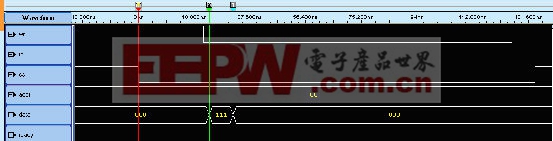

写HPIC的时序截图如下:

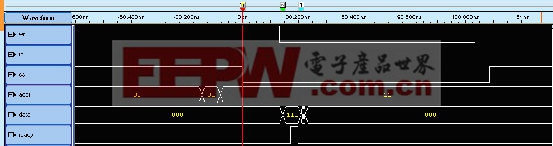

写HPID的时序截图如下:

两个时序图显示主机送出的数据111b 在HSTROBE(ARM_WR)的下降沿后,很快被改变成其它值000b.在写HPID 的时序截图中,第一个HSTROBE的下降后,HPI送出HRDY信号,然后数据线被改变,首先判断HPI对主机的命令做出了响应,通过HRDY信号的出现时机,说明HPI判断这是一个读操作,可以判断为HSTROBE的下降沿采样HR/W信号不正确。

从硬件连接来看,HSTROBE(HR/W)要采样HR/W,HCNTL0/1来判断主机命令, HR/W的与HSTROBE为同一信号源,且同为下降沿,HR/W与HSTROBE的下降沿之间的setup时间不够,采样HR/W的电平状态出现误判,认为是高电平读命令,HPI对读命令的响应则是在第一个HSTROBE的下降沿之后送出HRDY信号,并在HRDY之后,HPI送出数据到总线上。

对于该问题,需要对参与HSTROBE逻辑译码的HR/W信号的下降沿做延时处理,可在逻辑电路如CPLD或FPGA里实现,以确保HSTROBE的下降沿采样到稳定的HR/W电平。

评论