如何通过RTL分析、SDC约束和综合向导进行FPGA设计

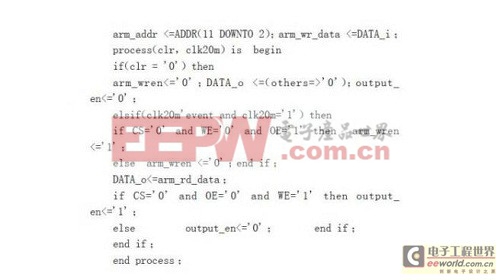

这里的解决方案是在综合的第一阶段(编译)后截取映射名称,在 BluePearl 软件套件的 SDC 生成工具中使用名称,并为综合工具的第二阶段(优化)提供适当的SDC。该方法给FPGA设计人员提供了一个最佳解决方案,无需花时间处理格式化问题。

能取得哪些实际的效果

Blue Pearl 软件套件能实现一些任务的自动化, 设计人员对其结果质量(QoR) 很满意。表 1 显示了用 Blue Pearl 软件套件自动生成SDC,能将示例设计的 QoR 提升 20%,该示例采用多个 IP 核,其中包括 Verilog 的R1200 和 VHDL 的 AES 加密。

对FPGA设计人员来说,降低压力、简化工作的一个好办法就是跟别人一样添加RTL分析、SDC 生成和综合向导工具。

评论