基于双机通信的研究

当SCE214 与S3C4510B 同时向同一存储单元( # 07FF) 写入数据时,如果对侧地址信号的稳态先于本侧的时,本侧 信号输出 L.,表示禁止本侧处理器写入,本侧写入脉冲中加入等待周期; 若对侧地址信号的稳态晚于本侧时,本侧

信号输出 L.,表示禁止本侧处理器写入,本侧写入脉冲中加入等待周期; 若对侧地址信号的稳态晚于本侧时,本侧 信号输出" H".,表示本侧处理器可以执行写入操作;

信号输出" H".,表示本侧处理器可以执行写入操作; 不能同时为" L".。

不能同时为" L".。

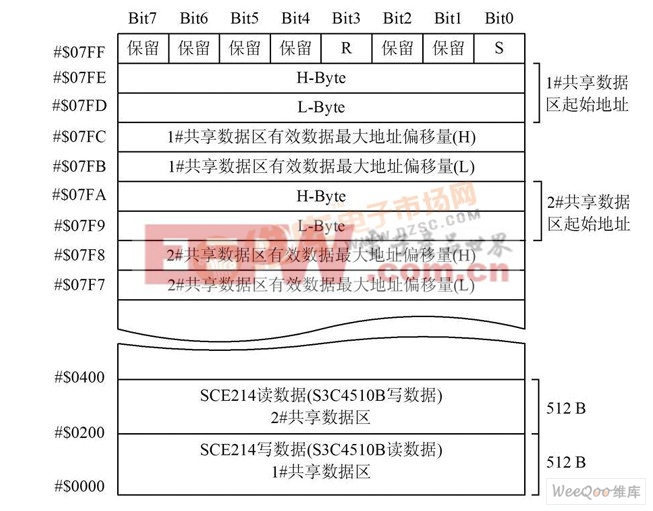

图6 是双口RAM IDT7132 存储器映射图,IDT7132 空间大小为2 KB,存储空间划分为两部分: 控制区和数据区。数据区分又分为两部分: 1# 区和2#区,其空间均为512 B,1# 区用于实现SCE214 写入数据和S3C4510B 读出数据,2# 区用于实现SCE214 读出数据和S3C4510B 写入数据。控制区包含读/ 写标志、1 # 数据区起始地址及有效数据最大地址偏移、2#数据区起始地址及有效数据最大地址偏移。

图6 双口RAM IDT7132 存储器映射图。

处理器对双口RAM 的操作过程如下:

( 1) SCE214 有写入数据时,将数据写入1# 区,有效数据起始地址写入$ 07FE、$ 07FD 存储单元中( 按小端格式存放) ,有效数据地址最大偏移量写入$ 07FC、$ 07FB,并将$ 07FF 的Bit0 置为1;( 2) S3C4510B 读双口RAM 时,先判断$ 07FF 的Bit0 是否为1,若为1,从$ 07FE、$ 07FD 存储单元中取出有效数据起始地址,从$ 07FC、$ 07FB 存储单元中取出有效数据地址最大偏移量,根据有效数据起始地址和最大偏移量,读出双口RAM 中的数据,并将$ 07FF 的Bit0 置为0;( 3) S3C4510B 读双口RAM 时,若判断出$ 07FF的Bit0 为0,则S3C4510B 认为SCE214 无数据发送来。这时S3C4510B 若有数据需要写入双口RAM,则将数据写入2# 区,有效数据起始地址写入$ 07FA、$ 07F9存储单元中( 按小端格式存放) ,有效数据地址最大偏移量写入$ 07F8、$ 07F7,并将$ 07FF 的Bit3 置为1;( 4) SCE214 轮循到读双口RAM 操作时,先判断$ 07FF 的Bit3 是否为1,若为1,从$ 07FA、$ 07F9 存储单元中取出有效数据起始地址,从$ 07F8、$ 07F7 存储单元中取出最后一个有效数据的地址偏移,根据有效数据起始地址和最大偏移量,读出双口RAM 中的数据,并将$ 07FF 的Bit3 置为0;( 5) SCE214 轮循到读双口RAM 操作时,若判断出$ 07FF 的Bit3 为0,SCE214 认为S3C4510B 无数据发送来。

如此重复( 1) ~ ( 5) 的操作,即可完成SCE214 与S3C4510B 的双向通信,最大一次可传送512 B数据。

2 结论

双机通信在嵌入式系统中应用比较广泛,本文介绍的设计方案主要用于速率要求高、成本适中的场合。

由于本系统采用的是双处理器结构设计,给系统的稳定性带来一定的隐患,有待于在以后的研发中能将双处理器集成为单片处理器。双网数字传真机研发的亮点在网络传真,其网络传真实现的业务不是实时传真,加之因特网本身的时延较大,有待用户检验,但其市场前景仍比较乐观。

参考文献:

[1].2K datasheethttp://www.dzsc.com/datasheet/2K+_2205217.html.

[2].S3C4510Bdatasheethttp://www.dzsc.com/datasheet/S3C4510B+_.html.

评论