基于DM642DSP的视频编码优化方法

-可以保证编码端的变换和解码端的反变换完全匹配,没有误差。

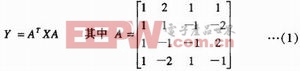

首先我们对变换矩阵做必要的调整,如表达式(1),(2)所示,这样做的好处是行变换和列变换的操作完全一样,简化了运算。接下来就是用线性汇编或纯汇编来实现两个矩阵的相乘。

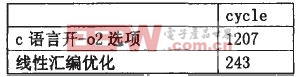

因为DM642CPU有两个类似的可进行数据处理的通路A和B,每个通路有4个完全相同的运算单元(.L,.S,.M,.D)我们可将矩阵的一四两行的运算放在A侧进行,二三两行在B侧进行运算,这样可以保证A,B两侧可同时并行计算。由于整数DCT变换是在16比特精度下完成的,矩阵相乘我们自然会想到汇编指令DOTP2,但是不能全部用DOTP2来完成运算,否则一个周期内就只有.M单元在工作,而其他运算单元都闲着。由于整数DCT矩阵系数的特殊性,我们完全可以用加法指令和移位指令来代替乘法指令。表1是一个16x16宏块进行DCT变换,汇编优化前后的cycle数的对比。

表一 16x16宏块DCT所需的周期数

在写汇编指令时我们要尽量做到在同一个周期内,让位于A,B两侧的8个运算单元能够同时工作,在做DCT时我们发现M单元不够用,而有时在其他情况下,M单元根本就没用上,这时就要想办法用M去代替其他运算单元。如求残差时要把8位数扩展成16位数,一般用UNPKLU4和UNPKHU4指令来完成,也可以用DOTPU4乘以0x01010101,同样也可以完成扩展要求。

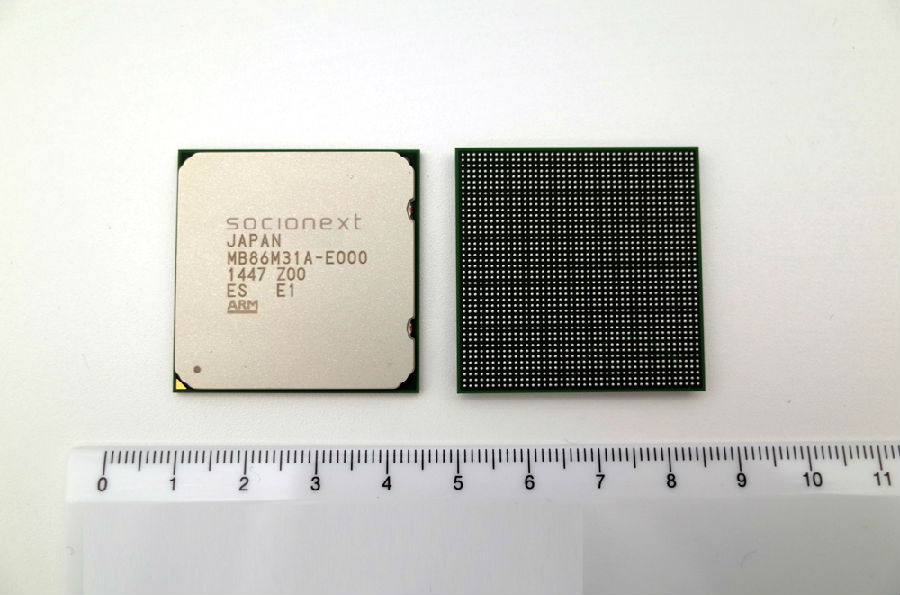

表二 H.264编码器性能测试

实验结果与总结

由于此编码器是针对监控系统的应用,在追求编码速度的时候,对图像质量做了一定的牺牲。下面是编码器的一些参数配置:图像皆为CIF大小,参考帧用了一帧,搜索范围是[-16,16],相邻两个P帧间插入两个B帧,即IBBPBBP……的编码方式,P帧和B帧做运动估计时最小块到8x8块,即只在16x16、16x8、8x16、8x8几种模式间做选择,量化步长设为30.。采用CAVLC编码方式。

本文针对实时视频监控的应用要求,结合DM642嵌入式系统的硬件特性,从程序的总体架构,数据的存放位置,数据的搬移进行了分析,给出了切实有效的优化方法。对占用系统资源较多的运动搜索给出了适合在DSP平台下的算法,对整数DCT进行了在汇编层面的优化,并总结了一下优化技巧。经测试基本达到视频监控的实时要求,并且有较好的图像质量和码率。

评论