短波信道模拟器中数字下变频的设计

图2 基于查表法的NCO 原理图

图2 中,32 位累加器由一个32 位的加法器和一个32 位寄存器组成,在时钟的作用下,加法器通过寄存器将输出数据送入到加法器的一个输入端,与32 位的频率控制字进行相加运算,得到一个有规律的相位累加结果。查找表实际上是一个存储了正弦信号抽样点幅度编码的只读存储器ROM,但ROM表的大小会随地址位数的增加成指数递增关系,因此,为了不减少查找表的地址位数而满足信号性能,必须采用优化方法来减小ROM 表的大小。根据正弦波的对称特性,只需存储四分之一周期的幅值,再通过相应的转换即可恢复出整个周期的幅值。同时,由于余弦波和正弦波相位差为??/ 2,可以很容易地实现余弦信号。

完成DDC 的NCO 模块设计后,将需要下变频的输入信号与NCO 产生的2 路正交本振信号进行相乘,完成数字混频正交变换,即完成频谱搬移。

2. 2 CIC 滤波器设计

CIC 积分梳状滤波器是实现高速抽取非常有效的单元。CIC 滤波器的单位冲激响应为:

从式( 2) 可以看出CIC 滤波器由2 部分组成,即积分器和梳状器级联组成,其实现非常简单,只有加减运算,没有乘法运算,FPGA 实现时可达到很高的处理速率。但是,单级CIC 滤波器的旁瓣电平只比主瓣低13. 46 dB,这就意味着阻带衰减很差,一般是难以满足实用要求的。为了降低旁瓣电平,可以采取多级CIC 滤波器级联的办法解决。

N 级CIC 滤波器级联的带内容差是单级CIC 滤波器带内容差的N 倍,这意味着多级CIC 滤波器级联增大阻带衰减的同时也增大了带内容差。所以,CIC 滤波器的级联数是有限的不宜超过5 级。

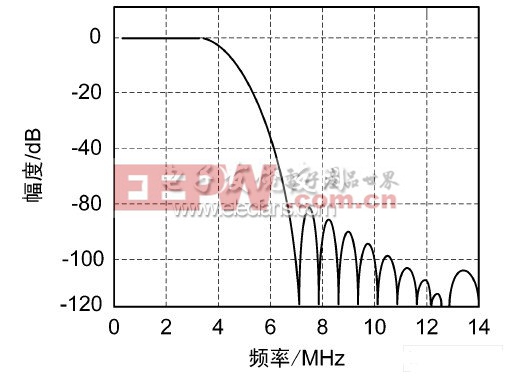

该设计中,CIC 滤波器需要完成16 倍的抽取,采用5 级级联来实现,输入和输出部分的位宽均为12 bit,在MATLAB 仿真的结果如图3 所示。

图3 CIC 滤波器幅度特性

经过CIC 滤波器后,信号采样速率经过16 倍抽取后变为4 MHz,从而实现了抽取功能,同时也降低了采样速率。

评论