基于DSP+CPLD 可重构数控系统的设计与仿真

(2).四轴编码器信号处理电路设计

四轴编码器信号处理电路是对光电编码器输出的两组相差90o 的方波信号的处理,从而获得执行元件实际位置,其输出是一路16 位的数字量,反馈给中央处理器,编码器信号处理电路包括滤波,倍频,计数几个功能模块,传统的四轴编码器信号处理电路采用分立元件来设计,它可靠性、抗干扰能力差,应用CPLD 设计了单片并行四轴编码器信号处理电路。

它具有实时性好,硬件体积小,工作效率高,提高系统的集成度,相对于分立元件,单片并行四轴编码信号处理电路集成在一个片子上,一方面单片芯片内的门电路、触发器的参数特性是完全一致的,在相同转速下脉冲信号的脉冲周期可以保持一致。另一方面,电路做在单个芯片内,抗干扰性能比分离器件构成的电路也有很大的提高,增强了系统的灵活性、通用性和可靠性。本文设计是一个四轴伺服系统,因此有八路四组方波信号,A 相B相相差90o,CLR,CLK,WE 分别为输出清零,系统时钟和输出使能,SEL*是输出选择信号,选择X,Y,Z,A中的一组信号处理的结果作为输出信号,分时送到数据总线。

滤波模块的设计

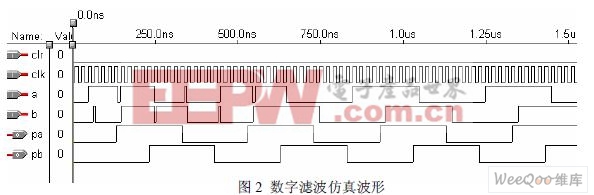

编码盘理论上是稳定的方波信号,但在实际操作中,经常会存在脉动干扰,滤波模块的功能是将这些脉动干扰滤掉,降低系统产生误动作的可能性,提高系统的可靠性,下面的VHDL 程序通过对A,B 两相方波信号同时延时四个CLK 脉冲,,脉冲宽度小于三个CLK脉冲周期的输入信号被滤掉。仿真结果如图:

倍频计数模块的设计

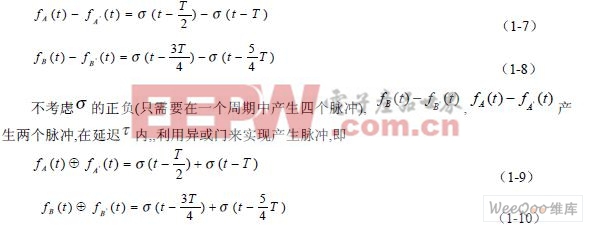

四倍频电路的设计是为了增加计数脉冲在一个周期中的个数,来提高测量的分辨率,工程中常把光电编码器输出的两路方波信号的上升沿和下降沿,来获得四倍频的脉冲信号,把光电编码器的分辨率提高四倍,通过光电编码器输出两路方波信号相差的正负来确定运动的方向,对光电编码器输出信号A、B;可以写成:

如图:

伺服电机相关文章:伺服电机工作原理

评论