基于FPGA的MC-CDMA基带系统的实现

2.2 系统时钟管理单元设计实现

为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驭动设计的主时钟,以达到最低的时钟抖动和延迟,本文中时钟管理单元的实现亦遵从这一原则。本文设计的系统时钟产生结构模块共使用3个Altera公司的OCMIP核来产生品振时钟的6种分频,输入时钟在第一个DCMIP核模块中经过一个IBIJFG后用来驱动第二个和第三个OCMIP核模块。

2.3 系统验证结果

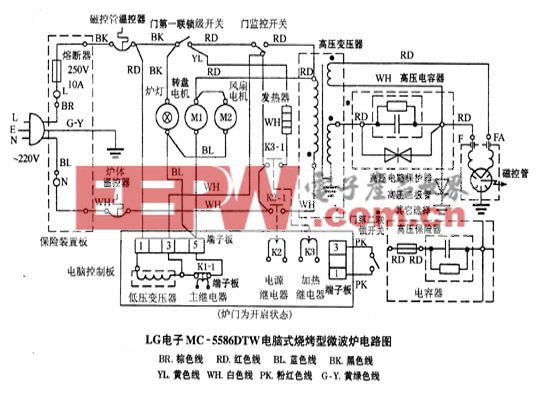

仿真条件设定为:单位比特信噪比EbNo=4,系统带宽B=20 MHz,OVSF扩频码字号K=31,采用ch=2时的信道参数组模拟信道,长信源随机信号的长度为L=T×len=2 000×15=30 000,单用户,AWGN信道。其中ErrorN为接收机统计所得的误码个数。图1是采用QPsK调制方式时系统联合调试的功能仿真结果,信宿模块统计得到的误码比特数ErrorN为602,BER==602/30 000=0.020 067,接近EbNo=4时的仿真结果0.020 05。

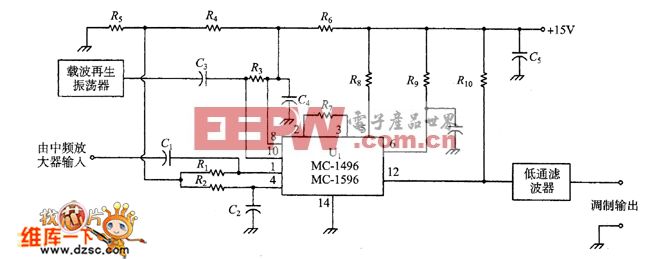

随着调制阶数的增加,系统的性能会有所下降,高阶调制对系统硬件的要求会更高。图2为使用Altera Quartus II 6.0仿真平台的综合工具得到的系统所占用的芯片资源情况。仿真所用的芯片与DE2开发板上的芯片一致,均为Altera公司Altera CycloneII。因为对运算过程中涉及的乘法和复乘运算进行了简化,并尽可能有效利用片内的定值模块,极大地减少了资源消耗量。本文引用地址://www.cghlg.com/article/191496.htm

本文首先提出了2发3收MIMO MC-CDMA基带系统的系统联合调试方案框架,使用硬件仿真MIMO信道模块来实现发射机和接收机的连接,设计了跨6个时钟域的系统时钟管理单元来实现各个模块之间的时钟同步,并详细介绍了时钟管理单元的设计实现方法与功能仿真结果。对FPGA基带系统进行联合调试,并与MATLAB仿真结果相比较,验证了发射机和接收机的功能,并将整个基带系统的RTL代码成功下载到DE2开发板的芯片上,调试成功。

参考文献

[1] 刘宝琴.可编程逻辑器件及其应用[B].北京:清华大学出版社,1995.

[2] Cyclone III device handbook:cyclone III device family overview.American.Altera Corp,2008.

cdma相关文章:cdma原理

评论