基于FPGA增量式编码器的接口设计与实现

对以上3种计数方法进行分析可知,用纯软件计数虽然电路简单,但是计数速度慢,微处理器工作量大,难以满足实时性要求,想得到更高的指标,只能不断地更换高性能微处理器,而且由于光电编码器的转速具有不可预见性,采用锁相环进行倍频的话会造成数据的不精确;而纯硬件电路体积大且稳定性、可靠性差、调试烦琐,而且当电阻、电容等组件参数变化时,会导致脉宽发生变化或不能产生具有稳定宽度

的脉冲。此外,RC电路抗干扰能力差,反馈部分易受外界干扰,在实际应用中会出现丢失脉冲现象,以至影响控制系统的精度和可靠性。

对于滤波、延时的处理方法很多,如微分型电路其信噪比小、抗干扰性差,积分型电路可以提高信噪比,但和微分型电路一样有缺点:当输入信号频率高时,电容充放电不及时,导致输出信号严重变形;对于各路倍频电路来说,电阻和电容的参数不可能完全一致,所以倍频后的各路脉冲宽度不等,而且宽度的调节也比较困难。设计采用的数字型延时电路可以很好地克服以上延时电路的缺点,延时的时间和各路倍频的脉冲宽度由时钟控制,倍频后的脉冲宽度均匀一致。本文引用地址://www.cghlg.com/article/190932.htm

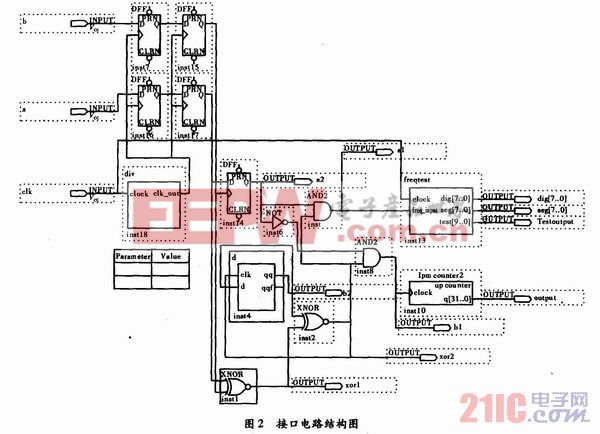

运用FPGA实现4倍频、鉴相电路,采用全数字反馈电路的设计方法,由于倍频、鉴相电路设计在同一芯片上,一方面,FPGA门电路高数量较大,时钟频率可达上百MHz的可编程逻辑器件,可以把他设计成所需的各种逻辑器件,可并行处理多项任务。因此处理速度比单片机或DSP快得多;另一方面,芯片内部的门电路、触发器的参数特性完全一致,能保证在相同转速下4倍频脉冲信号的周期保持一致。作为板级芯片,电路做在芯片内部,其抗干扰能力比分离器件有很大提高。同时,由于现场可编程,可以方便地实现对电路的重新设计或修改,增强了系统的灵活性、通用性和可靠性。

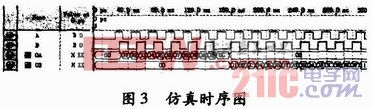

3 仿真波形

用Verilog HDL语言完成电路描述,各功能模块运用原理图方式进行描述,芯片采用Ahera公司Cyclone系列的EP1C12Q240C8N。在Quart-usII10.0环境下进行功能和时序仿真。编译后结果如图3所示,A、B即为差分整形电路的输出,当A相超前B相时,输出正向4倍频脉冲,OA[7..0]为编码器正转时4倍频脉冲个数;反之,输出反向4倍频脉冲,OB[7..0]为反转时4倍频脉冲个数。利用OA[7..0]与OB[7..0]可以方便地实现编码器的可逆计数。

4 结束语

设计了增量式光电编码器的一种简单且高精度的鉴相、计数和接口电路,可根据光电编码器的转向进行递增或递减计数,并可与PC机、DSP、ARM等器件直接进行并行通讯。实验结果验证了设计的正确性。可以看出,利用FPGA设计光电编码器信号处理模块,无论是设计过程,还是电路结构、都变得更加简洁。另外,在应用中注意FPGA的时钟周期应小于编码器脉冲的1/4,通常FPGA的时钟已远远小于编码器脉冲周期,故在FPGA中进行处理与计数是没问题的。

文中FPGA实现的编码器倍频、鉴相电路,已经在激光跟踪系统的项目中得到验证,在系统中存在抖动及毛刺等干扰的情况下,仍能获得稳定可靠的测量结果,并且可根据需要,任意改变参数以达到目的,这对正确和合理地使用编码器,提高功能效益,从而在数控及机器人的死循环位置和速度控制系统中,提高位置调节精度、扩大速度调节范围,都有良好的效果,是一种提高编码器分辨率、实现角位移或转速测量的优选电路。

评论