基于FPGA实现千兆以太网业务在SDH上的传输

在整个FPGA设计中,接收端的帧同步模块是比较重要的,它主要进行GFP帧的帧头搜索和同步保持处理。同步状态转移图如图3所示。本文引用地址://www.cghlg.com/article/190502.htm

用一个状态机表示三种状态,即搜索态、预同步态和同步态。在预同步状态和同步状态时都只取1帧进行状态跳转判断。状态机在FPGA初始化时默认处于搜索状态,然后在连续的GFP数据流中进行帧头的搜索判断,将连续的数据流在每个时钟周期按字节存入缓存器中,在每个时钟周期进行4 B的扰码判断,即连续的4个字节与扰码序列“B6AB31E0”进行异或,得到的4 B数据中前2个字节根据扰码多项式G(x)=X16+X12 +X5+1生成2个字节的校验值,然后与后2个字节进行比较,如果一致则表示找到了帧头,进入到预同步态。在预同步态继续在一帧帧头的相应时刻进行帧头的判断,如果正确则跳转到同步态,否则重新跳转到搜索态,继续寻找帧头。如果进入到同步态,和预同步态一样,也在一帧帧头的相应时刻进行判断,如果正确则继续保持在同步态,否则跳转到搜索态,重新在数据流中进行帧头的搜索。只有在处于同步状态时才能继续对数据进行后续处理。

在SDH和GFP协议的成帧解帧里都要进行扰码和解扰处理。SDH的扰码多项式为G(x)=X7+X6+1,GFP对核心头部PLI的扰码多项式为G(x)=X16 +X12+X5+1,GFP净负荷域的扰码多项式为G(x)=x43+1。这些扰码器都为串行扰码器,对于GE这种速率的数据如果也采用串行处理方式的话,FPGA内部是无法实现的。经过转换处理,可以将串行扰码器变为并行扰码器再进行扰码,即可降低处理速度,满足时序要求。

2 仿真综合及实现

本设计采用VHDL硬件描述语言,使用的是XILINX公司带有高速SERDES接口的SPARTAN-6芯片,利用ISE 12.1和仿真软件进行了综合和仿真。由于FPGA的内部资源较为丰富,本身自带的IP核具有可靠性、方便性和灵活性的特点。时钟部分使用了XIUNX芯片内部的DCM时钟管理模块,双端口RAM以及FIFO缓存器都使用了FPGA的内部IP核资源。高速数据接口部分使用的是芯片内部的GTP模块,去掉了外部高速接口转换芯片,简化了电路板的设计,不但提高了设计效率,也提高了系统设计的稳定性。

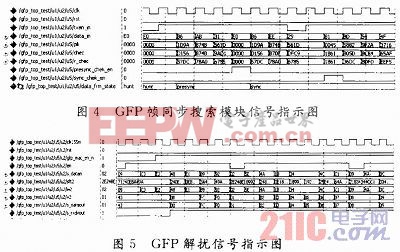

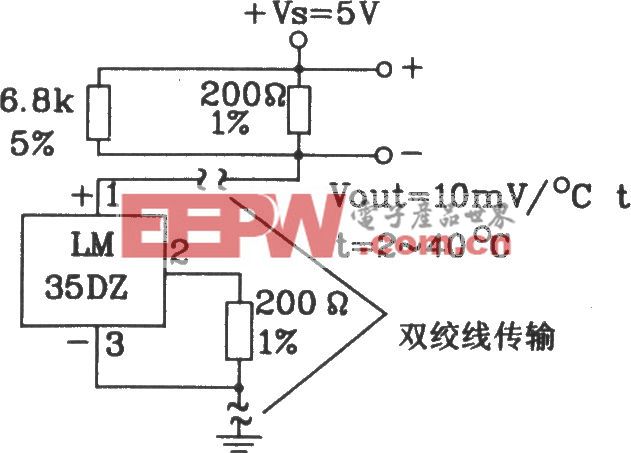

图4和图5表示的是对EOS数据进行VC-4-7V虚级联后的部分时序仿真图。

图4中,data_frm_state信号表示的是帧同步状态机。在数据流中,状态机一开始处于hunt状态,一旦找到帧头,则进入到presync状态;如果帧头检测没有错误,则继续跳转到sync状态;如果帧头判断正确,那么状态机就一直保持在sync状态。

图5中,s_datain信号表示的是解码前的数据,s_dataout信号表示的是根据扰码多项式G(x)=X43+1解扰后的数据。

3 结语

综上所述,利用FPGA可以实现千兆以太网MAC帧在SDH数据帧中的封装和映射,配合外围接口电路的使用,可以实现GE在STM-16中的传输。EOS技术既增强了以太网传输的覆盖范围,也丰富了SDH设备的传输接口,极大地方便了用户的使用。同时,利用FPGA进行设计,大大缩短了开发的周期,也便于以后的升级和维护。

评论