短波扩频猝发通信系统的DSP+FPGA实现方案

TMS320VC5509和TMS320VC33的互通

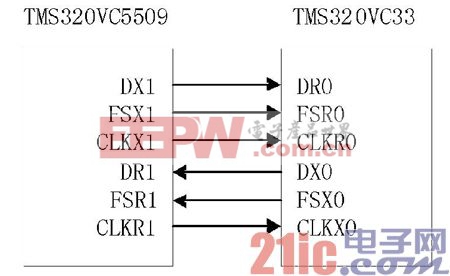

本方案采用的是用DSP串口来实现TMS320VC5509和TMS320VC33之间的通信。由于TMS320VC5509的多通道缓冲串口远比TMS320VC33的串行口功能强大,设置灵活,所以在设计的时候我们就考虑将TMS320VC5509的串口设为主方,TMS320VC33的串口设为从方,连接图如图4所示。

将TMS320VC5509内部采样速率发生器的输入参考时钟设置为CPU时钟,通过对CPU时钟的分频来得到串口移位时钟和帧同步信号,并由TMS320VC5509提供收发双方的移位时钟,而帧同步信号则由发送方提供。同时将TMS320VC33设置为标准模式、固定速率的工作方式,与TMS320VC5509的串口匹配。通过双方设置可以进行每帧16bit或32bit的传输。这样双方DSP可以通过握手,采用中断或查询方式来进行数据的高速收发,并且还可以灵活地对双方串口的工作方式进行改进。

下面给出TMS320VC5509多通道缓冲串口及TMS320VC33串行口通信的关键程序段。

TMS320V

C5509多通道缓冲串口初始化程序:

MOV #0x0000,PORT(#SPCR2_1) ;采用多通道缓冲模式

MOV #0x0000,PORT(#SPCR1_1)

MOV #0x0040,PORT(#RCR1_1) ;接收每帧1个阶段,每阶段1个字,字长

MOV #0X0001,PORT(#RCR2_1) ;16比特,不压扩,1比特延迟

MOV #0x0040,PORT(#XCR1_1) ;发送每帧1个阶段,每阶段1个字,字长

MOV #0X0001,PORT(#XCR2_1) ;16比特,不压扩,1比特延迟

MOV #0x0003,PORT(#SRGR1_1) ;脉宽1个clkr/x,clkr/x为4分频(最大)

MOV #0x200f,PORT(#SRGR2_1)

MOV #0x0B00,PORT(#PCR1) ; fsr设为输入

MOV #0x0040,PORT(#SPCR2_1) ;GRST=1,启动采样速率发生器

MOV #0x00c0,PORT(#SPCR2_1) ;FRST=1,启动帧同步

MOV #0x00c1,PORT(#SPCR2_1) ;XRST=1,启动发送器

MOV #0x0001,PORT(#SPCR1_1) ;RRST=1,启动接收器

TMS320VC33串行口初始化程序:

LDI @p0_addr,ar0 ;p0_addr=808040h 总体控制寄存器

LDI 331h,r1 ;FSX/DX 设定为输出 CLKX设定为输入

STI r1,*+ar0(2) ;FSX/DX/CLKX串口控制寄存器

LDI 111h,r1 ;FSR/DR/CLKR设定为输入

STI r1,*+ar0(3) ;FSR/DR/CLKR串口控制寄存器

LDI @p0_global,r1 ;00e940004h 固定速率 标准模式 16bit STI r1,*ar0

LDI @buff_rec,ar7 ;接收缓冲区

LDI 020h,ie ;CPU串行端口0接收中断启用

STIR1,*+AR0(8) ;AR0指向串行端口总体控制寄存器(00808040h)

结束语

现代通信技术和超大规模集成电路以及高速信号处理器的高速发展,使得短波猝发扩频通信在军事通信中极具潜力。本文给出了一种DS-QPSK短波扩频猝发通信的系统实现方案,并运用TMS320VC33、TMS320VC5509和ALTERA公司的Cyclone系列FPGA构建的硬件平台进行了DSP+FPGA的混合硬件实现,得到的系统性能已达到预期的要求,实现了数据的有效实时处理。

评论