一种数字无线收发系统设计

2.2 本振

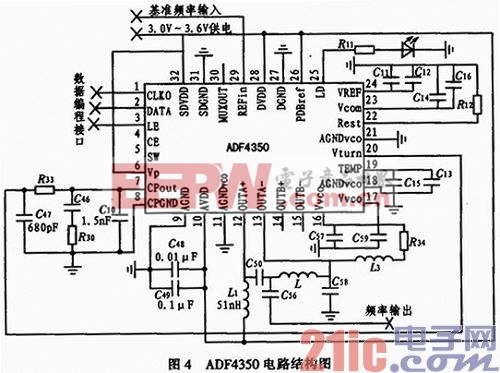

收发系统中频率源为混频器提供本振信号,要求频率源输出频率稳定度高。ADF4350是ADI公司的集成VCO(压控振荡器)宽带频率合成器,输出频率范围137.5~4 400 MHz。ADF4350需结合外部参考源以及环路滤波器使用,可实现小数N分频或整数N分频。片内寄存器均通过简单的三线借口进行控制。参考源频率由16 M晶振提供,选择合适的分频参数,通过单片机对寄存器进行操作,ADS软件进行环路滤波器仿真后得到422.2 M的本振频率。电路图如图4所示。本文引用地址://www.cghlg.com/article/189705.htm

2.3 混频器

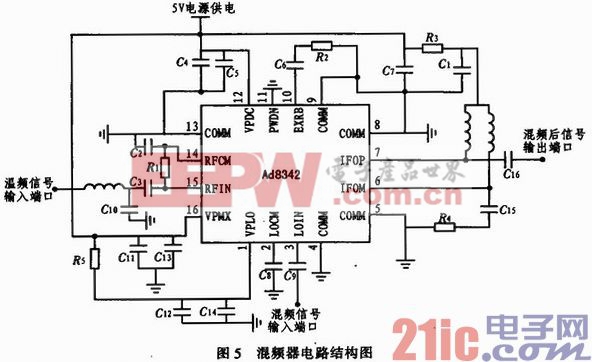

输出信号频率等于两输入信号频率之和、差或为两者其他组合的电路。ADI公司生产的AD8342芯片是一款集成有源宽带混频芯片,各个信号端口的输入输出频率范围都能够达到LF-3 GHz,中频(IF)端为差分输出,单端阻抗为50 Ω,电路图如图5所示。

2.4 放大器模块

在发射系统中,在混频器经过滤波后的放大器,将混频器输出的功率较小的433.92 MHz信号放大到适当功率,使后面的功放工作在最佳状态。输出功率的设计指标(500 mW)末级功放需要首先被确定,末级功放使用了高线性度的中功率功放AH102,增益约为12 dB,输出功率27 dBm,而混频器的输出功率约为0 dBm,所以放大器的增益要求要高于15 dB,输出1 dB压缩点高于15 dBm,才能保证输出功率。SGA-4586是RFMD生产的一款HBT可级联增益组件,其工作频率范围为DC-4000 MH。工作在433 M时,增益大于25 dB,放大器内部已为输入输出端口做了50 Ω匹配,外围只要连接必要的供电电路、RFC电路、隔直电路即可正常工作。另一个是射频功率放大器(RFPA),经过前级SGA-4586放大器放大后,再输入到末级功率放大器,获得足够的射频功率以后,才能馈送到天线上辐射出去。设计中要求末级输出功率要达到500 mW,所以功放的选择要选择最大输出功率大于500mW,即OP-1 dB要大于27 dBm,工作鞭率覆盖433.92 MHz,增益足够大的芯片。AH102的工作频段为350~3 000MHz,供电电压为8.5 V时,电流大小为260mA,功率2.21 W,此时输出功率537 mW(27.3 dBm),所以功效热损耗为1.67 W,功放模块必须加装散热片,保证功放芯片的温度不至于过高。

在接收系统中的低噪声放大器(LNA),一种位于放大链路输入端,针对给定的增益要求,引入尽可能小的内都噪声,并在输出端得到最大可能的信噪比而设计的放大器。接收机接入的LNA是为了对天线接收的微弱信号进行放大,再对信号做相应的处理。SPF-5043是RFMD公司生产的高性能晶体管单片微波集成电路低噪声放大器,应用频率50~4 000 MHz。当工作在433 M时,增益大于18 dB。噪声系数低于0.8 dB。输入输出端口皆有内部匹配,接上耦合电容即可。

3 数字中频处理器

与传统的超外差接收机相比,数字中频结构,在发送端,基带信号经过内插、滤波,I/Q调制后,进行D/A变换,变成中频模拟信号。在接收端ADC直接对中频信号进行采样,采样后由数字下变频进行I/Q解调、抽取、滤波、然后送往基带处理。

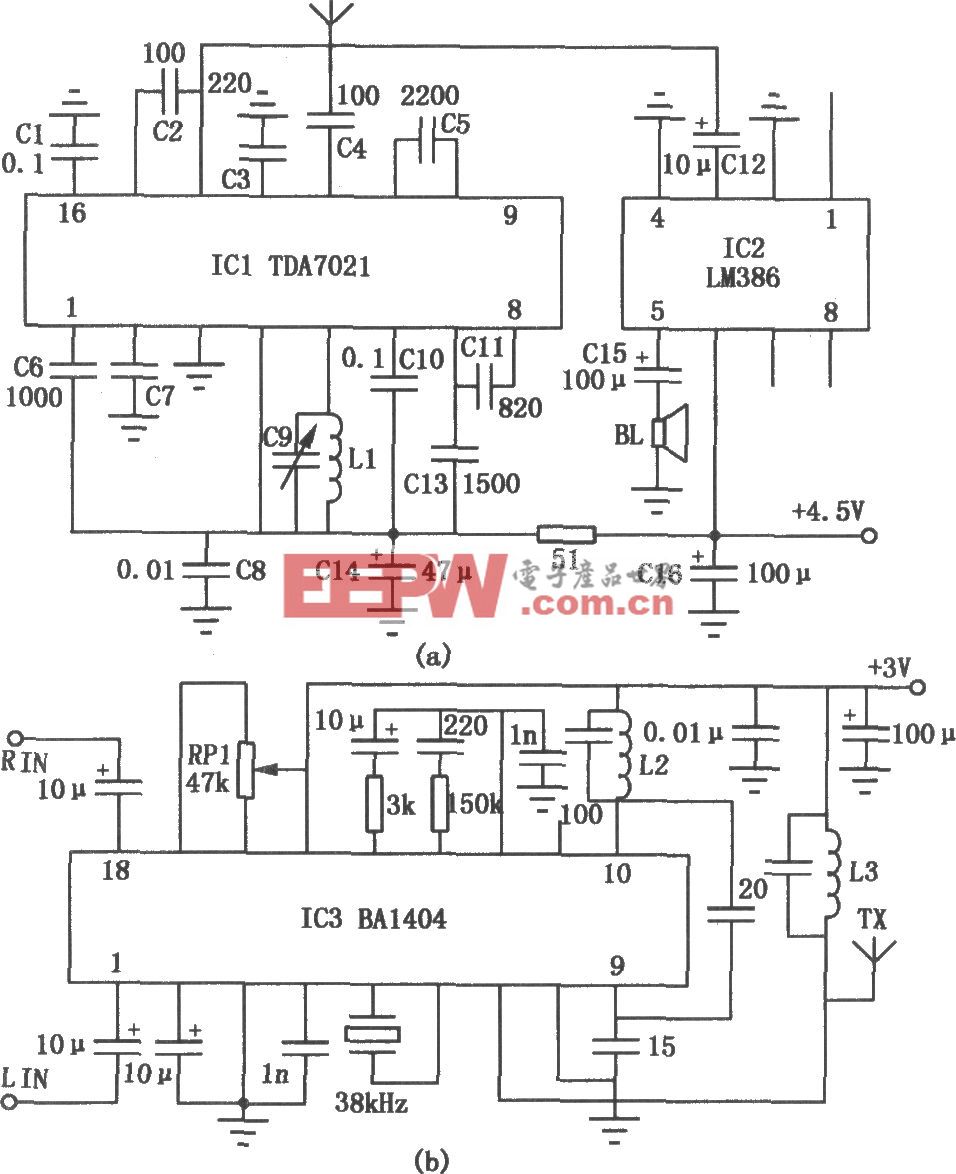

3.1 FM调制

如图6所示为FM信号发生器在FPGA中的实现框图,频率控制字A控制调制信号频率,B控制载波中心频率。相位累加器由加法器和寄存器组成,总的调制原理就是,周期变化的调制信号作用于控制载波频率的相位累加器B原本固定的步长,是总的步长产生周期性变化,从而实现载波频率在中心频率附近的周期变化,得到FM信号。表达式:y(t)=sin[(2πPfclk/2N)(△+2NPmsinωt/2πPfclk)]t,其中fclk为输入时钟频率,锁相环频率系数为P,计数器位数N。只需要把产生信号频率为fc的基础上把步长△改变为△+2NPmsinωt/2πPfclk,把2NPmsinωt/2πPfclk整体进行查表处理,同时频偏控制字Pm的计算,Pm=2π×△fmax,其中△fmax为允许的最大频偏。

滤波器相关文章:滤波器原理

pa相关文章:pa是什么

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

混频器相关文章:混频器原理 晶振相关文章:晶振原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论