基于Altera MegaCore实现FFT的方法

3 FFT运算器的实现

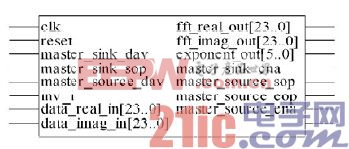

FFT 运算器采用FFT MegaCore 实现,用Quartus Ⅱ仿真软件设计时产生的FFT MegaCore 模块图如图4 所示[5]。这里采用器件为Altera 公司的Stratix 系列,变化域长度设置为6 4 ,数据量精度为2 4 b i t ,旋转因子量化精度为24bit。引擎结构可以选四输出,I/O数据流结构选连续型[3]。在工程中,设计者也可以根据实际情况选择其他的参数设置。

图4 FFT MegaCore模块

在F P G A 硬件设计中,一个乘法器占用的资源要远大于一个加法器占用的资源,而该模块主要是完成复数乘法运算,我们则可以通过数学变换减少乘法器的数量。例如两个复数a+jb 和c+jd 的乘积结果e+jf,其中e=ac-bd,f=ad+bc,变换得e=(a+b)c-b(c+d),f=(a+b)c-a(c-d),可以看出实际上是增加三个加法器来减少一个乘法器。

FFT MegaCore 端口定义如下。

clk:输入,FFT 系统时钟信号;

reset:输入,FFT高有效同步复位信号,低时FFT工作;

master_sink_dav:输入,指示主接收器数据有效信号;

master_sink_sop:输入,输入数据包起始位置指示信号;

inv_i:输入,转换方向控制信号,低有效时做FFT,高有效时做IFFT;

data_real_in[23..0]:输入,输入实部数据;

data_imag_in[23..0]:输入,输入虚部数据;

master_source_dav:输入,指示FFT 模块收到的数据是否有效;

master_sink_ena:输出,指示数据是否写入输入缓存中;

fft_real_out[23..0]:输出,输出实部数据;

fft_imag_out[23..0]:输出,输出虚部数据;

master_source_ena:输出,指示输出数据是否有效;

master_source_sop:输出,输出数据包起始位置指示信号;

master_source_eop:输出,输出数据包结束位置指示信号;

exponent_out[5..0]:输出,每一个数据输出时的一个比例因子,用来保持数据精度和内部最大信噪比。工作流程:系统复位后,数据源将master_sink_dav 置位,表示有数据等待输入;作为回应FFT Core 将master_sink_ena 置位,表示可以接收数据;数据源加在第一个复数数据,同时master_sink_sop 置位,表示输入数据包起始位置;下一个时钟,master_sink_sop 被清零,输入数据按顺序加入,输入数据达到设置值时,系统启动FFT 运算。通过inv_i 信号的置位和清零可以改变单个数据包的FFT 转换方向,inv_i必须与master_sink_sop严格同步。当FFT转换结束时master_source_ena置位,输出运算结果;在输出过程中master_source_sop和master_source_eop信号被置位,表示输出数据包的起始位置和结束位置;e x p o n e n t_out 为比例因子,是IP Core 通过每一次参数的设定自动计算出来的,对于每个数据包来讲,它产生的e x p o n e n t_out 的值是不同的。

4 结 论

本文介绍了一种采用Altera 公司的FFT MegaCore 实现快速傅里叶变换的方法,该方法非常简单,能进一层次简化开发的流程,缩短工程开发周期,节约成本,因此在实际工程中是一种很好的应用。

评论