多惯组脉冲输出同步计数系统设计

2.2 时钟分频模块设计

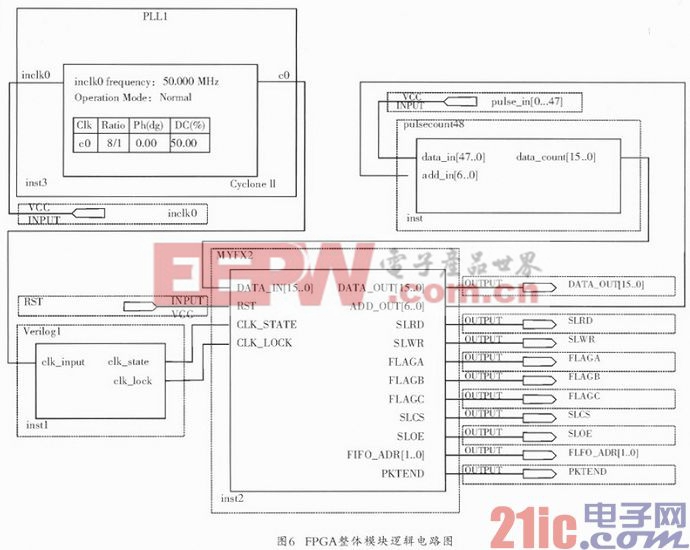

本系统采用50 MHz有源晶振,EP2C8Q208C8N内部拥有两个锁相环,通过倍频使频率达到400MHz,然后连接一个分频模块为状态机提供周期为4ms的计数值锁存信号(clk_lock)和一个状态机跳转触发信号(clk_state)。

2.3 状态机模块设计

状态机模块主要包括两个部分:数据处理部分和FIFO控制逻辑部分。

2.3.1 状态机的数据处理部分

状态机在计数值锁存信号(clk_lock)上升沿到来时会锁存计数器此刻的计数值,并在状态机的下一个状态将计数值存储到data-new的寄存器型变量中并进行求差运算,接着将被减数与减数在下一个状态进行更新,最后将求出来的差值交给FIFO控制逻辑进行发送。每个计数单元计数值求差的状态机原理图如图3所示。本文引用地址://www.cghlg.com/article/189660.htm

2.3.2 状态机的FIFO控制逻辑部分

FPGA控制逻辑的主要作用足通过其内部的状态机直接操作CY68013的FIFO来进行读写控制。SLOE、SLRD和SLWR作为芯片的读写信号与使能控制信号。INPKTEND是FPGA主动命令USB芯片向上位PC发送数据的控制端(当FIFO上的数据小于规定大小而又要强制上传给PC时使用)。FD为双向的数据传输接口。FLAGA、FLAGB、FLAGC、FLAGD四个标志位能够指示FIFO的空满程度,为数据的连续存取提供了可靠的保证。FPGA_ADR0和FPGA ADR1用于选择内部4个缓冲端点之一。IFCLK提供时钟信号(仅用于同步Slave FIFOs模式)。FPGA的引脚控制这些端口,达到对USB端的存储FIFO进行操作的目的。由于异步Slave FIFOs模式的读写状态简单,稳定性好。本系统选择异步方式来读取FIFO。

实现异步Slave FIFO的写操作的状态机如图7所示。其状态转移进程如下:

IDLE:此状态为空闲状态,什么也不做;当写事件发牛时(即CLK_LOCK的上升沿到来时),进状态1;

状态1:使FIFOADR[1:0]指向IN FIFO(即就是选择CY68013的四个大数据量FIFO中的一个,固件程序已将此FIFO配置为写模式),进状态2;

状态2:如果FIFO满标志为假(即FLAGC引脚为高电平时),则进状态3;否则在本状态等待;

状态3:驱动数据到数据线上,使SLWR有效(低电平),一个CLK_STATE后再无效(高电平),以使FIFO写指针递增,进状态4;

状态4:如需传输更多的数,返回状态2,否则进状态IDLE。

状态跳转示意图如图4所示:

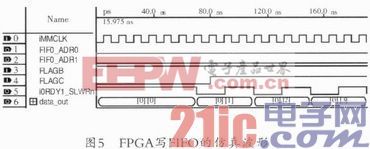

使用QuartusII对FIFO的控制逻辑进行时序仿真如图5所示。

2.4 FPGA整体模块设计

FPGA整体模块逻辑电路图如图6所示。

评论