基于FPGA协处理器的算法加速的实现

C代码转换到HDL

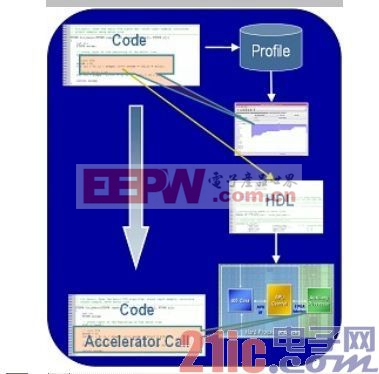

采用C到HDL的转换工具将C代码转换到HDL加速器是一种创建硬件协处理器的高效方法。图2所示以及下面详述的步骤总结了C到HDL转换的过程:

图2:C-HDL设计流程

1. 使用标准C工具实现应用程序或算法。开发一种软件测试向量(test bench)用于基线性能和正确性(主机或台式电脑仿真)测试。使用一种编译器(例如gprof)来开始确定关键的函数。

2. 确定是否浮点到定点转换适当。使用库或宏来辅助这种转换,使用一个基线测试向量来分析性能和准确性。使用编译器来重新评估关键函数。

3. 使用C到HDL转换工具(如Impulse C),在每个关键功能上重复,以实现:将算法分割成并行的进程;创建硬件/软件进程接口(流、共享存储器、信号);对关键的代码段(例如内部代码循环)进行自动优化和并行化;使用桌面电脑仿真、周期准确的C仿真以及实际的在系统测试对得到的并行算法进行测试和验证。

4. 使用C到HDL转换工具将关键的代码段转换到HDL协处理器。

5. 将协处理器连接到APU接口用于最终的测试。

Impulse:C到HDL转换工具

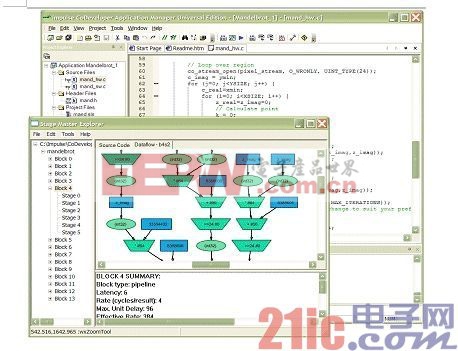

如图3所示的Impulse C通过结合使用C兼容库函数与Impulse CoDeveloper C代码到硬件的编译器,使嵌入式系统设计工程师能创建高度并行的、FPGA加速的应用。Impulse C通过使用定义完好的数据通信、消息传递和同步处理机制,简化了硬件/软件混合应用设计。Impulse C提供了C代码(例如循环流水线处理、展开和运算符调度)的自动优化以及交互式工具,允许你对每个周期的硬件行为进行分析。

图3. Impulse C

Impulse C设计用于面向数据流的应用,但是它也具有足够的灵活性来支持其他的编程模型,包括使用共享存储器。这一点很重要,因为基于FPGA不同的应用具有不同的性能和数据要求。在一些应用中,通过块存储器读和写在嵌入式处理器和FPGA之间转移数据是有意义的;在其它的情况下,流传数通信信道可能提供更高的性能。可以快速建模、编译和评估可选的算法的能力对于实现某个应用最佳的结果来说,非常重要。

到目前为止,Impulse C库包含以新数据类型和预定义的函数调用形式的最少C语言扩展。使用Impulse C函数调用,你可以定义多个并行程序段(调用进程),并使用流、信号和其他机制描述它们的互连。Impulse C编译器将这些C语言进程转换并优化成:可以综合到FPGA的较低级HDL,或可以通过广泛存在的C交叉编译器编译到支持的微处理器上标准C(带相关的库调用)。

完整的CoDeveloper开发环境包括与标准C编译器和调试器(包括微软公司的Visual Studio和GCC/GDB)兼容的台式电脑仿真库。使用这些库,Impulse C程序设计工程师能编译和执行他们用于算法验证和调试目的的应用程序。C程序设计工程师还能检验并行进程,分析数据移动,并利用CoDeveloper Application Monitor解决进程到进程的通信问题。

在编译时,Impulse C应用的输出是一组硬件和软件源文件,用于输入到FPGA综合工具。这些文件包括:

1. 用于描述编译硬件进程的自动产生的HDL文件;

2. 用于描述连接硬件进程到系统总线所需的流、信号和存储器组件的自动产生的HDL文件;

3. 自动产生的软件组件(包括运行时间库)用于建立任何硬件/软件流连接的软件端;

4. 附加文件,包括脚本文件,用于输入产生的应用程序到目标FPGA布局布线环境。这种编译进程的结果是一个完整的应用,包括需要的硬件/软件接口,用于在基于FPGA的编程平台上实现。

评论