基于挠性覆铜箔的平面无源集成LC单元设计

本文引用地址://www.cghlg.com/article/187773.htm

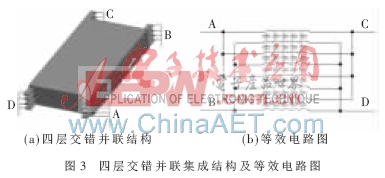

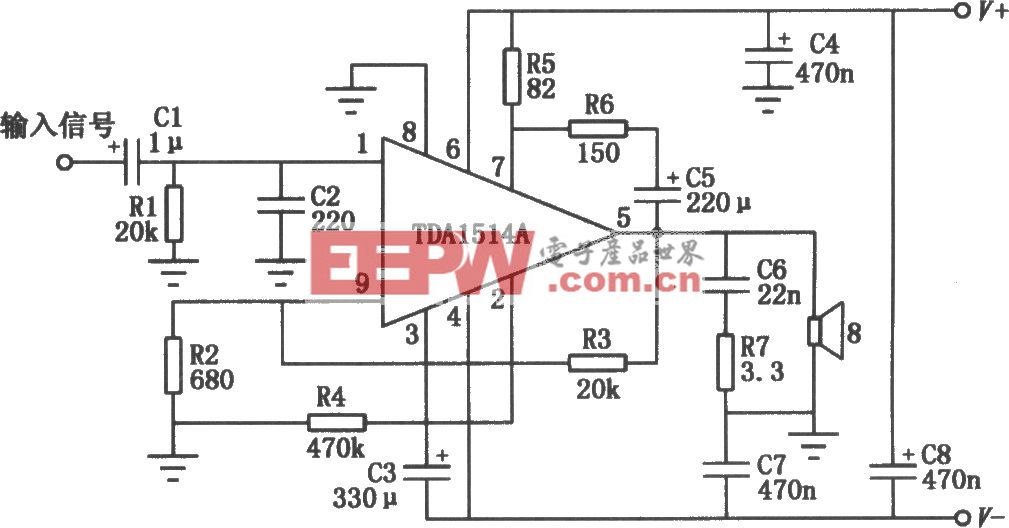

本文引用地址://www.cghlg.com/article/187773.htm本文提出了一种基于多层挠性覆铜箔交错并联的平面集成LC结构,实现了串/并联谐振的集成。如同图2制作方式一样,共裁剪8片这样的形状,把它们层叠、紧压,能够实现交错并联集成的LC单元结构,这种结构能灵活增大电容,如图3(a)所示,其等效电路如图3(b)所示。同样也是4个端子的LC单元结构,可以制作多个这样的集成LC单元,按照参考文献[2]提到的多个单元连接结构还可以根据不同电感值和电容值的需要,对多个单元进行大电感大电容、大电感小电容、小电感大电容、小电感小电容的串/并联连接来实现。进一步增加了集成电感值和电容值的灵活性。

本文先制作2个四层交错并联集成的LC单元。采用CI型磁芯,节省了EI型磁芯的磁芯中柱,增大了电容面积。将与CI型磁芯相应的电路板挖空,然后把每个集成LC单元的4个引脚焊接到电路板上,2个单元之间的引线可以从电路板上走线,磁芯扣在LC单元上,既可以节省整体无源器件所占空间体积,还可以增大磁芯的散热面积。若想增大电感值,当给集成LC单元通电时,所有集成LC单元电流的方向应该是一个方向,比如每个集成LC单元都从A、D端输入,从B、C端输出,连接方式可以在电路板上实现;而若想减小电感值,可以使若干集成LC单元电流流向相反,即从B、C端输入,从A、D端输出。结构示意图如图4所示。

1.2 电容的计算

由式(1)可以看出,如果需要增加更大的电容C,有3种途径:(1)增大电介质材料的相对介电常数 ?着r;(2)增大平面绕组的铜箔面积 w;(3)减少电介质材料的厚度d。

若增加更大的电容,采用交错并联方式[1]优势即可显现出来,如图2(b)所示,假如每个单元由n片这样的结构叠加成图3(a)的结构,可以推导出电容C的计算公式:

同样在计算电感时,先计算一个集成LC单元的电感量,根据参考文献[2],多个单元根据需要可通过不同的连接方式得到不同的电感值。

2 仿真和实验

本文制作了一台基于交错并联挠性覆铜箔材料的集成谐振LC单元样机,如图5所示。该样机选用天通公司的CI14/13磁芯;集成LC单元的材料选用咸阳众鑫电子材料有限公司的挠性覆铜箔聚酯薄膜。具体参数如表1所示。

集成LC单元的制作方式如图3所示,制作的2个四层集成LC单元,测得每个集成LC单元的电感值为3.6 ?滋H,电容值为0.37 nF,按照参考文献[2]中大电感大电容的串联方式连接计算得到电感为14.3μH、电容为0.83 nF。按照大电感大电容的并联方式连接得到电感值为57.1 μH、电容为0.21 nF,样机计算的参数如表2所示。

评论