TIP41C低频大功率平面晶体管芯片设计

2.2 基区宽度Wb和发射结结深xje的确定

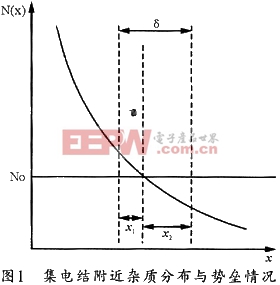

低频大功率晶体管的Wb、xje主要根据击穿电压和安全工作的需要来选定。图1是集电结附近的杂质分布和势垒情况,其中x1和x2分别是集电结在基区部分和集电区部分的势垒宽度,它们的总势垒宽度是δ=x1+x2。这样,在NC为2×1014cm-3、NSB为1018 cm-3、V为280 V的条件下,查表可得δ=35μm,x1/δ=0.07,此时x1为2.45μm。

为了保证击穿电压的要求,应尽可能的提高二次击穿耐压量,晶体管的基区宽度应大于2.45μm,但又不能太大,否则基区输运系数η会减小。从而使电流放大系数减小,因此应选择基区宽度Wb=3μm。由于集电结结深xjc=Wb+xje=8μm,因此,一般来说,发射结xje应等于基区宽度的 1.0~2.5倍。综合以上考虑,可确定基区宽度Wb为3μm,发射结结深xje为5μm。

2.3 外延层厚度T的确定

外延层厚度T至少应等于集电区厚度WC、集电结结深xje、反扩散层三部分之和。为了能达到BVCBO指标,集电区高阻层厚度WC应大于为集电结雪崩击穿时对应的空间电荷宽度XmB。

评论