LD0、QLDO、VLDO的设计原理及测试介绍

2 VLDO的设计原理本文引用地址://www.cghlg.com/article/176478.htm

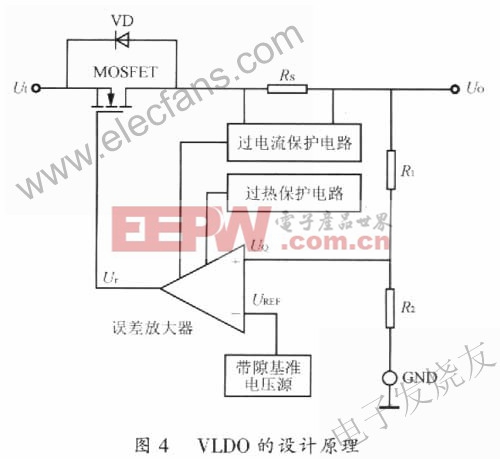

VLDO的设计原理如图4所示,典型产品为Analogic TECH公司的AAT3200。VLD0的最大特点是采用P沟道功率场效应管MOSFET来代替PNP型功率管作为调整管,MOSFET本身还带保护二极管(VD)。P沟道MOSFET属于电压控制型器件,其栅极驱动电流板小,而通态电阻非常低,通态压降远低于双极性晶体管的饱和压降,这不仅能大大降低输入-输出压差,还能在微封装下输出更大的电流。图4中还给出了内部过电流及过热保护电路,RS为电流检测电阻。

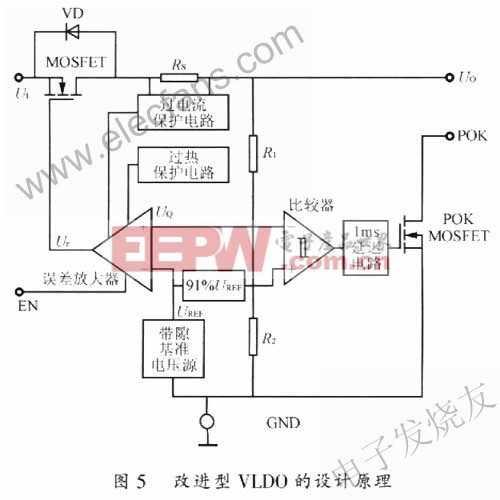

一种改进型VLDO的设计原理如图5所示。其主要特点是增加了输出状态自检(POK)、延迟供电、电源关断等功能。POK(Power OK)是表示“电源正常”的信号。一旦输出电压降低到使采样电压低于9l%UREF时,比较器就输出高电平,经过l ms的延迟时间强迫POK MOSFET导通,从POK端输出低电平(表示电源电压过低),送至微处理器。当输出电压恢复正F常叫,比较器输出低电平,令POK MOSFET截止,POK端输出为高电平,以此表示电源正常。POK MOSFET采用开漏极输出结构,外部需经过lO kΩ~l MΩ的上拉电阻接U0端。不用POK端时可接地或悬空。EN为使能控制端,当EN端接低电半时将电源关断。LDO进入休眠状态,此时POK端 呈高阻态。利用延迟电路能避免因干扰而造成的误动作。

评论