基于87C51FB单片机的跳频控制器的设计与实现

1 引言

本文引用地址://www.cghlg.com/article/172070.htm跳频就是“多频、选码、频移键控”,即用伪码序列构成跳频指令来控制频率合成器,并在多个频率中进行选择的移频键控。

跳频通信具有抗干扰、抗截获的能力,并能做到频谱资源共享,所以,在当前现代化的电子战中,跳频通信已显示出巨大的优越性,它是战术无线电通信抗干扰措施的具体体现。另外,跳频通信也正应用到民用通信中,以抗衰落、抗多径、抗网间干扰和提高频谱利用率。

跳频控制器是跳频通信系统中的核心部件,具有跳频图案的产生、同步、自适应控制等功能。我们研制了超短波跳频通信系统中的跳频控制器。下面详细讨论其设计与实现。

2.1 主要技术参数设计

考察一下系统的跳频技术性能,主要注意下列各项指标:跳频带宽要宽,跳频的频率数目要多,跳频的速率要快,跳频码的周期要长,跳频系统的同步时间要短。

所设计的跳频控制器的主要性能指标如下:

跳频速率:203跳/ s;

跳频带宽:可在30MHz~87.975MHz范围跳,也可分段跳;

跳频频率数:256个;

组网能力:能组128个网,有迟入网功能;

同步:首次同步时间0.5s,迟后入网同步时间为6s;

同步可靠性:误码率10-1时,同步概率为95%;

跳频图案:复杂非线性;

跳频序列周期:>1011bit;

跳频密钥量:>264;

语音数据速率:16kb/s。

2.2 硬件系统的设计

2.2.1 硬件电路组成

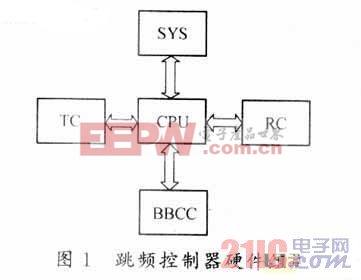

整机电路如图1所示。

它有五个主要模块,其功能简要说明如下。

(1)微处理器模块(CPU)

是跳频控制器的核心,CPU产生信号控制整个跳频控制器工作。它由87C51FB单片机及外围电路组成。

(2)基带模块(BBCC)

给收发信机模块和音频单元之间进出的发送和接收信号选定通路。BBCC模块含有下列微电子模块:

射频音频接口(RAI);

增量调制器(DM);

先入先出(FIFO)控制器(FC);

Bit同步器(BIS):使跳频控制器的内部数据时钟与接收数据同步;

伪随机码发生器(PRG):产生确定跳频图案的码,受CPU模块控制。

(3)接收模块(RC)

搜综接收数据以得到同步数据,它包含下列微电子模块;

相关器:将收到的数据和CPU模块提供的数据序列(相关码)进行比较,在相一致(相关)时作出指示;

同步检测器和TOD(Time of Day)解码器(SYTD):译码同步数据并提供指示得到同步的定时信号,还译码TOD数据并将译出数据送CPU模块,SYTD由CPU模块控制;

实时时钟(RTC):当电源由跳频控制器断开时,这块微电子电路保持TOD的跟踪。跟控器电源断开时,一块锂电池给RTC馈电,由一个32.768kHz振荡器作为RTC频率基准。

(4)定时模块(TC)

提供定时控制信号。

(5)系统模块(SYS)

使系统的跳频控制单元和其他单元接口。

2.2.2 跳频控制器工作原理

首先介绍跳频控制器发送通路的工作原理。

(1)数字化的发送信号加到FC的串入并出寄存器,FC把发送数据组织为16bit一组。当二个数据字节准备好时,FC对CPU发信号,CPU读取两个字节,并把它们存入作为FIFO寄存器的RAM部分。FIFO控制器的工作起点与跳频周期(用信号HOP表示)的起点同步。

(2)FC还包括一个8bit并入串出寄存器。送到收发信机模块去的数据从该寄存器取出。在发送同步序列期间和频率变换期间,从FC的串入并出寄存器来的数据积累在作为FIFO的RAM部分中。

(3)以信号FOUT-STOPPED(频率为18.3kHz)为时钟将FC的并入串出寄存器的数据字节移出。移出的速率(18.3kHz)高于数据装入 FC的速率(16kHz),这两个数据速率之差允许CPU把同步数据插入发送数据流中,并在频率变换期间停止发送数据。

(4)由FC移出的数据送到射频音频接口RAI模块。RAI对发送信号滤波并把得到的信号TXBBR加到收发信机模块系统连接器。

下面再叙述跳频控制器接收通路的工作原理。

(1)RAI把接收信号RXBBR通到位同步器BIS、相关器COR,并经线性均衡器加到FC。

(2)COR将接收的数据和CPU提供的基准序列进行逐bit的比较,当一致bit数大于CPU提供的门限时,COR给出相关脉冲。

(3)正相关脉冲和负相关脉冲加到位于RC模块的SYTD微电子模块。SYTD监视正相关脉冲,以便检测同步序列。当检测到同步序列时,SYTD产生信号S4。S4的出现受一窗口信号W2的控制。

(4)bit同步器BIS使跳频控制器的接收时钟FOUT与接收数据的实际时钟速率同步。在收发信机模块的4ms换频间隔期间和接收同步数据时,一窗口信号W1堵塞FOUT信号。

(5)FC把接收数据送到FIFO寄存器,然后从FIFO寄存器送到RAI或DM。接收方式时FC的工作方式和发送方式时的相反,即,数据以18.3kHz速率注入控制器,并以16kHz速率从控制器读出。

(6)出现在FC输出端的串序数据加到DM。DM把数据变换成模拟信号,并送到RAI。

评论