超低抖动时钟合成器的设计挑战

图3给出了4GHz VCO (UMX-806-D16)最差情况下的相噪和我们的目标相噪模板。该VCO在20kHz以下的相噪很高,但通过设计锁相环滤波器带宽可以抑制低频偏VCO噪声。假设没有其它因素的影响,可以得到很好的10kHz以上的相噪指标。请注意,这些相噪要求来自2GHz振荡器。然而,图3给出的是4GHz振荡器的曲线,它需要额外的2分频来保证50%的占空比。假设2分频自身不影响总相噪,将使VCO的相噪降低6dB,整个曲线平行下移6dB。

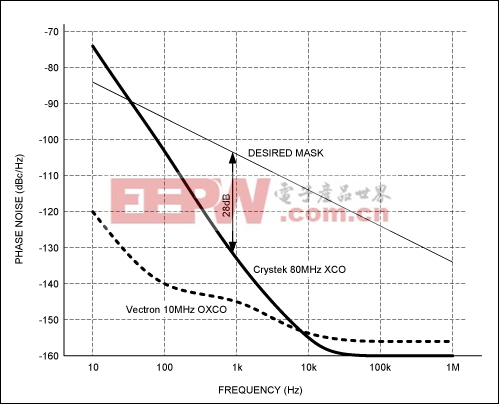

请注意,参考时钟也会产生噪声,但多数分布在环路滤波器带宽以下。图4给出了Crystek®的80MHz晶体压控振荡器的伯特图和目标相噪模板。注意,锁相环频率增益将等倍放大参考时钟的相噪。因此,对80MHz晶体和2GHz输出,其增益为25。结果,Crystek曲线将上移28dB。该平移意味着参考时钟的相噪在1kHz非常高³。然而,相噪模板假定总噪声功率在频偏以内均匀分布。当然,情况不一定是这样,所以1kHz以外的恒定相噪加上1kHz以内的噪声仍然可以满足我们的抖动指标。

图4. 参考时钟的相噪

图4的相噪分析还包括了Vectron恒温控制振荡器(OCXO),具有极低相噪。注意,OCXO容易消耗更多功率(达到瓦特量级)。

本文引用地址://www.cghlg.com/article/161856.htm

合成器原理图

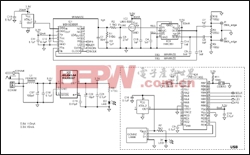

图5是前面讨论的参考时钟和VCO的完整电路原理图。PLL采用Fujitsu® MB15E06SR,它集成了4mA电荷泵和最高3GHz的预分频器。由于PLL需要编程,所以我们采用了一个很简单的PIC微处理器(PIC18F2455),内置USB接口,可以自动执行编程任务。该设计需要用软件编程用户界面,同时PIC也需要编程。

清晰图片(PDF, 93.8KB)

图5. 时钟合成器原理图

分频器采用Hittite® HMC361,它可以工作至10GHz,其相噪对性能影响不大。然而,分频器的输出摆幅只有0.8VP-P,即50Ω时2dBm。设计目标是10dBm输出(2VP-P),所以Hittite的输出不能满足要求,需要提升电压。On Semiconductor®或Zarlink®都有类似产品,但它们的输出摆幅基本和Hittite相同,甚至更差。而且,它们的噪声指标没有明确标出。

一个简单的变压器可以用来增大低速时钟的摆幅,但高于2GHz、可以实现4:1放大的变压器并不常见。另外,这种办法增加了阻抗设计难度。另一种方法是采用有源放大器,可以得到很多带宽> 10GHz的差分放大器,但还需要进一步确定器件的噪声指标,以满足设计要求。另一问题是放大器是否能够置于PLL,Fujitsu数据资料建议最大预分频输入为2dBm (1VP-P)。

仿真结果

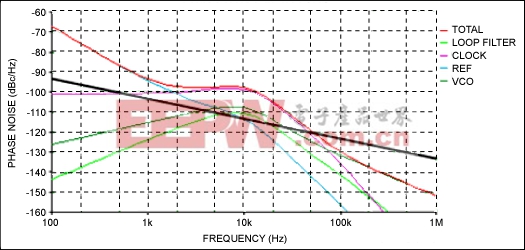

ADIsimPLL (由Applied Radio Labs为Analog Devices编写)可以用来分析该电路,它包括多个UMC的VCO模型。图6给出了由不带分频器的UMC 4GHz VCO和Crystek振荡器组成的PLL相噪伯特图。2kHz以下,参考时钟的噪声占主导地位;2kHz以上,鉴相器相噪占主导地位;70kHz以上,VCO噪声占主导地位。

图6包括了图2的目标噪声模板(粗黑线)。显然,总噪声在50kHz以下超出了模板,这将产生200fs的抖动。实际仿真存在一个问题,即如何解决鉴相器的相噪。它应该等于特定器件的噪底(-219dBc/Hz)乘以VCO/PFD频率,即4000MHz/25MHz,或44dB,平移118dB。还需进一步的核查,但即使将PFD (鉴相器)噪声去除,该结果仍然不可接受(167fs)。

图6. 使用VCO的仿真结果:4GHz下的相噪

评论