基于Nios II的UART与PC间的数据通信

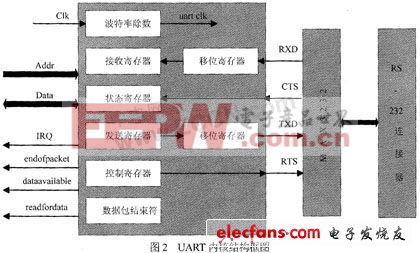

接收寄存器Rxdata保存接收到的数据。新字符由RXD输入,完全接收后状态寄存器的接收准备好RRDY位置1。当从接收数据寄存器读取数据后,状态寄存器RRDY位清零。若RRDY位为1时,又有字符输入,则发生溢出错误,状态寄存器的接收溢出错误ROE位置1。不管前一个字符是否被读出,新字符总是传到接收数据寄存器。

发送寄存器Txdata上的字符数据由Avalon主控制器发送,当将字符写入发送寄存器时,发送准备好TRDY位为0;当将字符从发送数据寄存器传输到发送移位寄存器时,TRDY位置1。如果在TRDY位为0时将字符写入发送数据寄存器,结果是未知的。

状态寄存器Status的状态位反映UART内核状态情况。每个状态位与控制寄存器中的对应中断使能位相联系。状态寄存器可以在任何时候读取。

控制寄存器Control由控制UART内核操作的控制位组成,控制寄存器的每一位使能状态寄存器中对应位的中断。当状态位及其对应的中断使能位为1时,UART内核产生一个中断。

除数寄存器Divisor的值用于生成波特率时钟。

数据包结束字符Endofpacket由数据包结束符寄存其的值确定,以便可变长度的DMA传输。

UART内核的寄存器映射表如表1所列。

2 串行异步通信软件的实现

为了适应系统不同类型的需要,UART驱动程序提供两种方式:快速型和一般型。快速型驱动程序采用中断驱动方式,在设备不准备发送或接收数据时它允许处理器执行其他任务。由于UART数据率相对于处理器的速率较慢,快速驱动程序可以提供系统的处理性能。一般型驱动程序采用查询执行方式,它在发送和接收每个字符前等待UART硬件的指示。

对于Nios II处理器用户来说,Altera提供硬件抽象层HAL系统库驱动程序,HAL系统库API函数为Nios II处理器用户提供访问UART内核的完整特性。程序设计所涉及到的API函数如下:

(1) alt_avalon_uart_init

定义:void alt_avalon_uart_init(alt_avalon_uart_dev*dev,void*base,alt_u32 irq)

功能:用于初始化UART设备

(2) alt_avalon_uart_ioctl

定义:int alt_avalon_uart_ioctl(alt_fd*fd,int req,void*arg)

功能:处理基于HAL的程序请求设备指定的操作

(3) alr_avalon_uart_irq

定义:static void alt_avalon_uart_irq(void*context,alt_u32 id)

功能:处理UART的中断操作

(4) alt_avalon_uart_read

定义:int alt_avalon uart_read(alt_fd*fd,char*ptr,int len)

功能:从UART中读取数据

(5) alt_avalon_uart_write

定义:int alt_avalon_uart_write(alt fd*fd,const char*ptr,int len)

功能:写一组数据到UART

以上几个函数完全可以满足UART与PC之间的数据通信,需要注意的是如果一次传输的数据过长,必须重新设置ALT_AVALON_UART_BUF_LEN的值,以保证传输过程中数据的正确性。如果此值过小,则在传输过程中可能会造成数据的丢失。在设置输出终端时必须指定COM1/COM2端口,建立UART与PC之间的数据通路,用来接收从UART中发出的数据,同时通过这些端口从PC中发出数据到UART中。

本文所述的UART是基于Altera公司的一款主流低成本的FPGA,除了具有FPGA的优势之外,还因为其CPU本身是以软核的方式实现的,所以整个系统的功能可以根据需要进行功能定制,非常灵活。

分频器相关文章:分频器原理

评论