I2C总线接口逻辑分析

3 I2C总线接口逻辑的构成

3.1 I2C总线接口电路的结构

I2C总线接口逻辑框图如图5所示。

在电路设计中,各功能块的硬件实现介绍如下。

启动、停止检测电路应用两个D触发器来分别响应SDA在SCL为高电平时的电平跳变。

移位寄存器电路由9个D触发器串联成9级移位寄存器,包括8位字节和1位应答位,实现SDA上数据的串并行转换。寄存器复位值为“111111110”,接收8位字节后为“0D7D6D5D4D3D2D1D0”,即应答位为“0”,在第9个时钟时输出低电平作为应答信号。

可编程地址发生器电路生成器件地址,7位器件地址由器件编号地址(高4位)和引脚地址(低3位)组成。通过改变器件引脚的连接方式,就可改变器件地址,因此使应用方便灵活。

地址比较器电路由门电路组成布尔代数式逻辑,对寻址字节进行判断。若地址正确则将RS触发器置“1”,使能译码器输出。

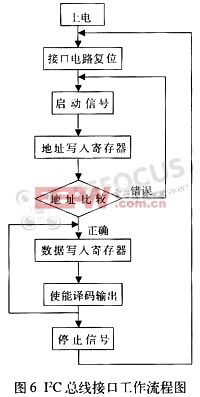

3.2 I2C总线接口工作流程

I2C总线接口工作流程如图6所示。

评论